# ARM's processor lines

# Dezső Sima

## November 2018

(v3.2)

© Dezső Sima 2018

#### ARM's processor lines

- 1. Evolution of ARM

- 2. Evolution of the ARM ISA

- 3. Overview of ARM's processor families

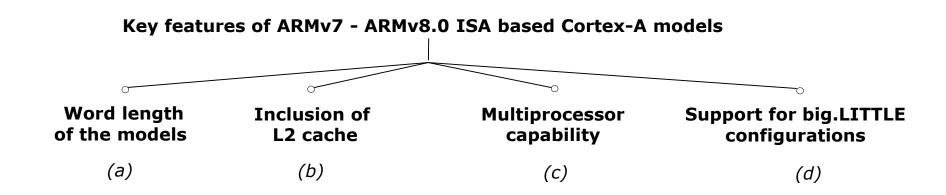

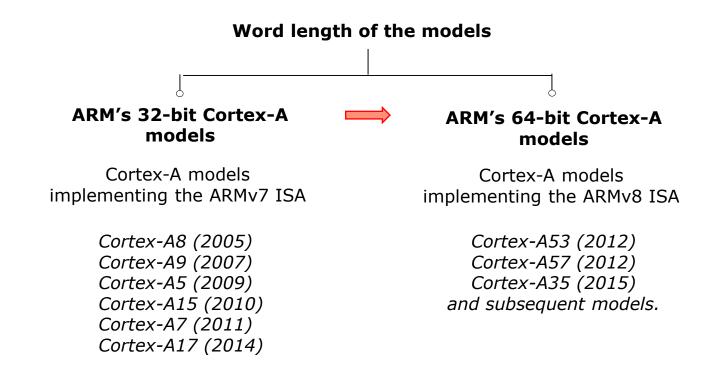

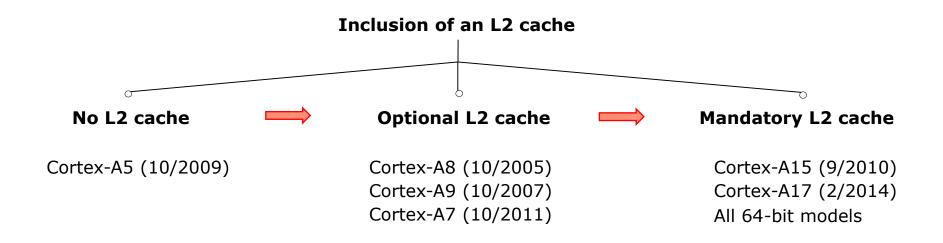

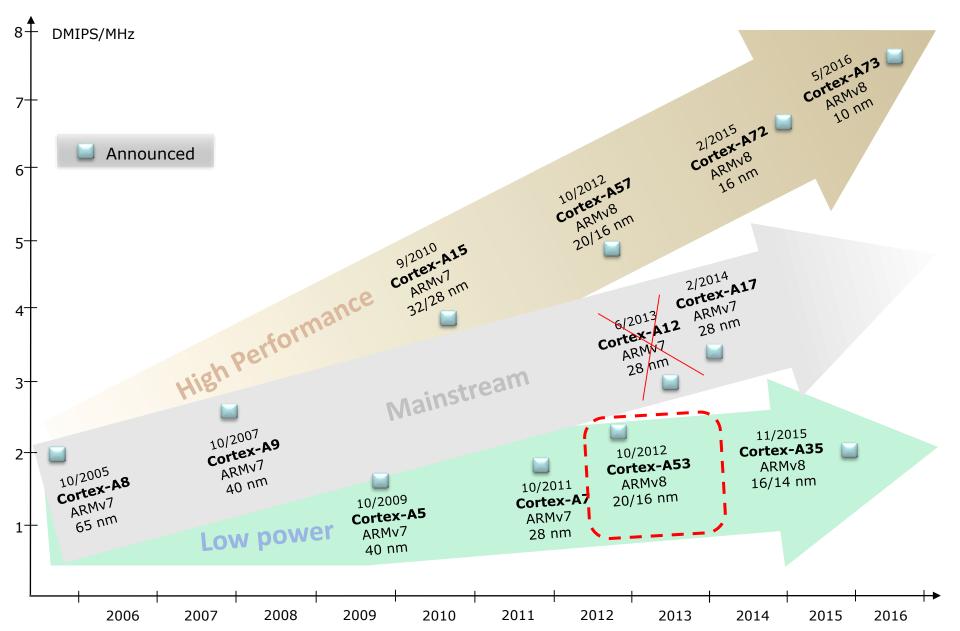

- 4. Evolution of the Cortex-A series ARMv7/v8.0 ISA-based models

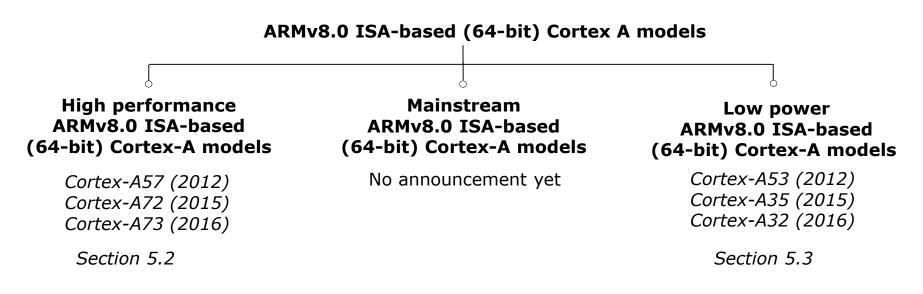

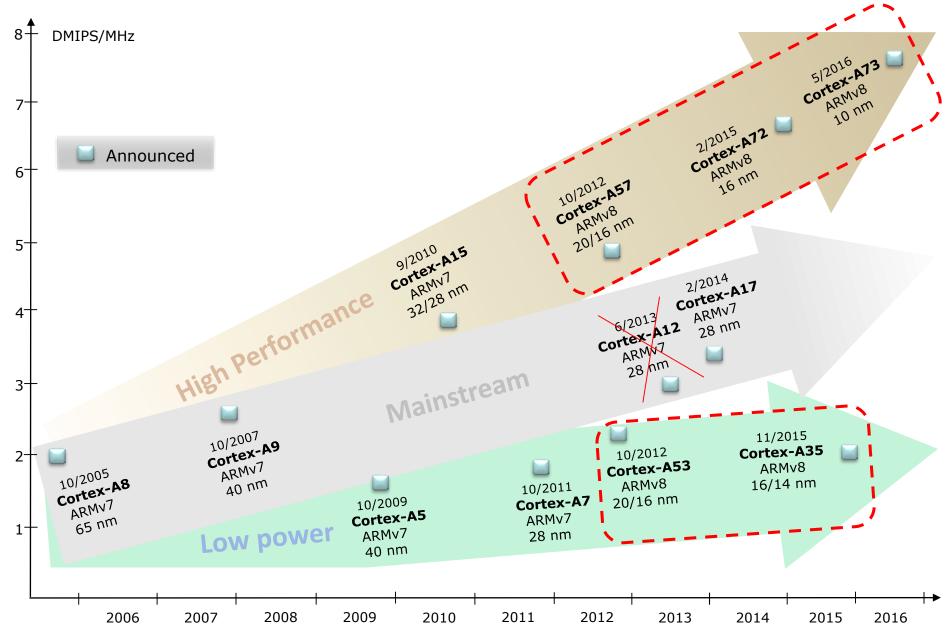

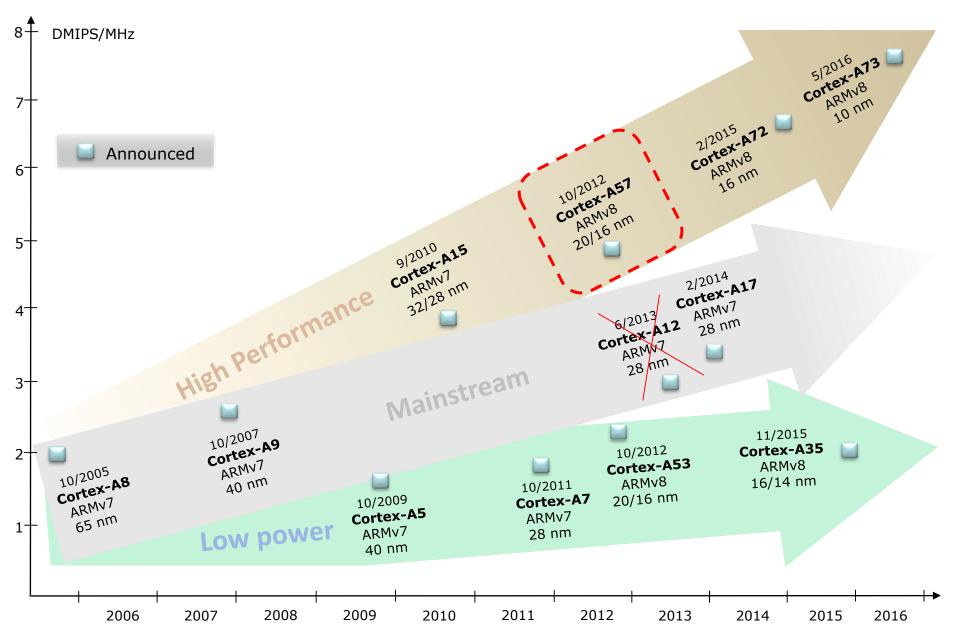

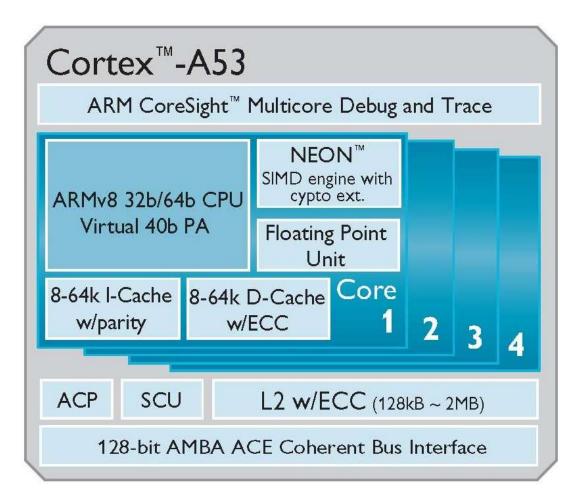

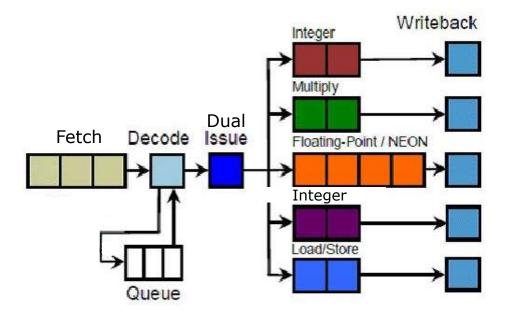

- 5. Cortex-A models based on the ARMv8.0 ISA

- 6. Cortex-A models based on the ARMv8.2 ISA

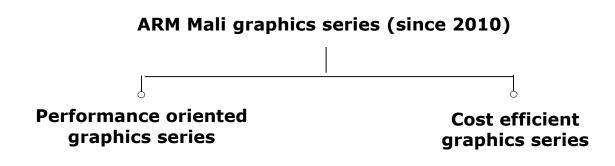

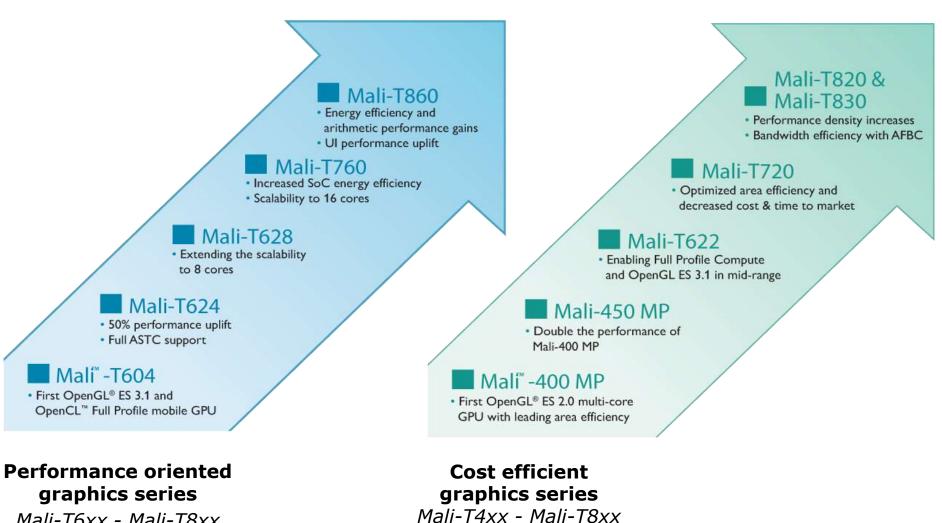

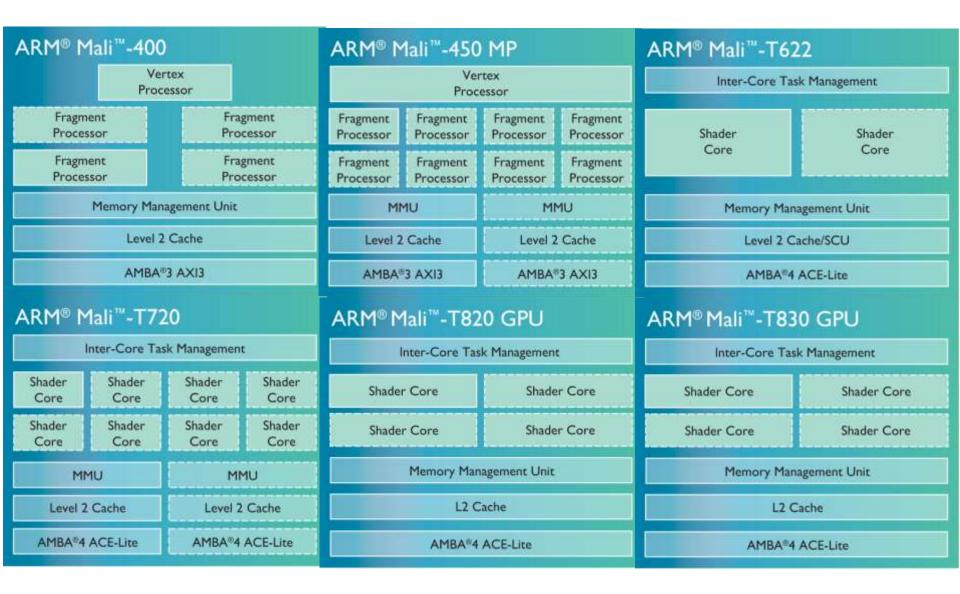

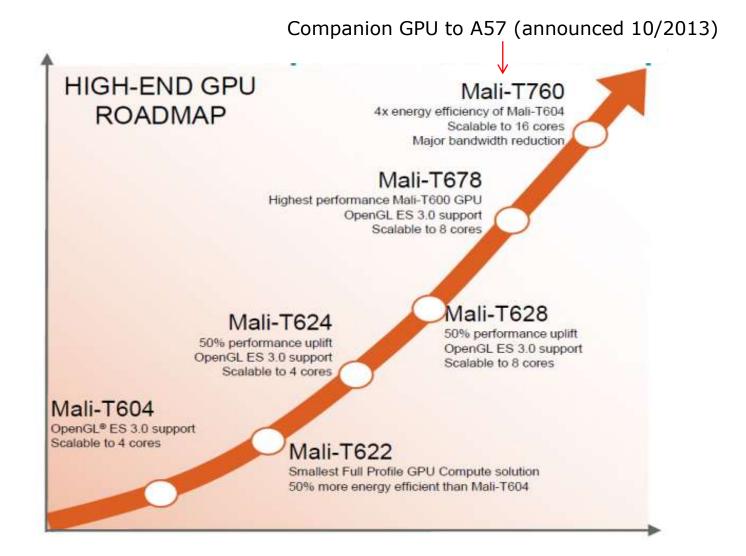

- 7. Overview of ARM's Mali graphics series

- 8. References

#### Note

In the Lecture (Fall 2018) only the following Sections will be discussed:

Section 1: Evolution of ARM

From Section 2: Evolution of the ARM ISA

2.1: Overview

From Section 2.2: ISA extensions introduced to enhance compute capabilities

2.2.1: Overview

Section 3.4: Processors implementing the ARM v7 - ARM v8 ISA

Section 4: Evolution of the Cortex-A series models that are based on the ARMv7/v8.0 ISA

Section 6: Cortex-A models based on the ARMv8.2 ISA

## 1. Evolution of ARM

- 1. Evolution of ARM

- ARM (ARM Holdings plc) is a British multinational semiconductor company with its head office in Cambridge, acquired by Softbank (Japan) in 2016.

- The company

- designs low power

- ARM processors for the embedded, mobile and server market,

- mobile GPUs (termed as Mali GPUs) as well as

- design tools (development studios etc.),

- and licences

- their IP (Intellectual Property) including their ISA but does not fabricate semiconductors.

plc: public limited company (a.m. kft) intellectual property: a.m. szellemi tulajdon \*

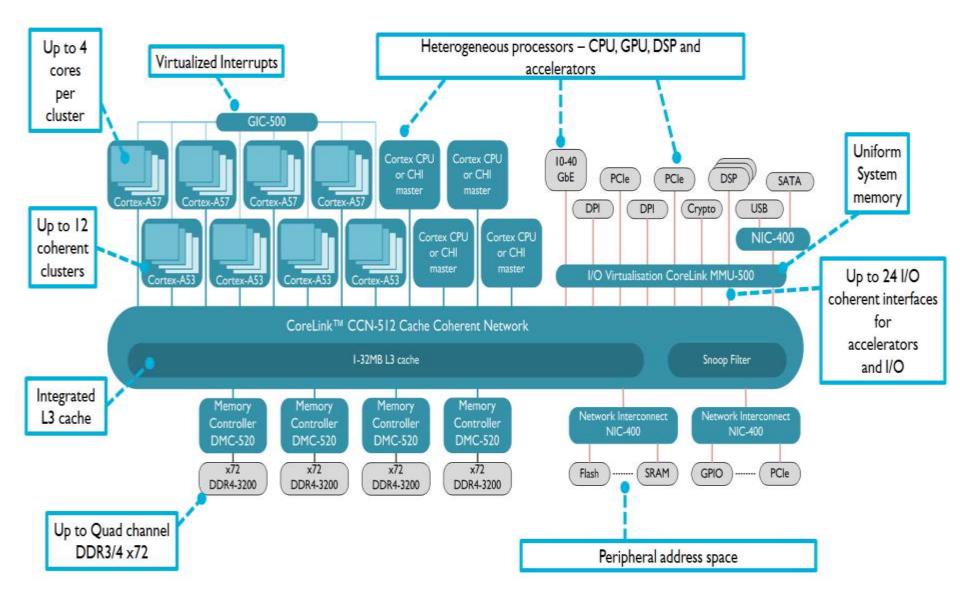

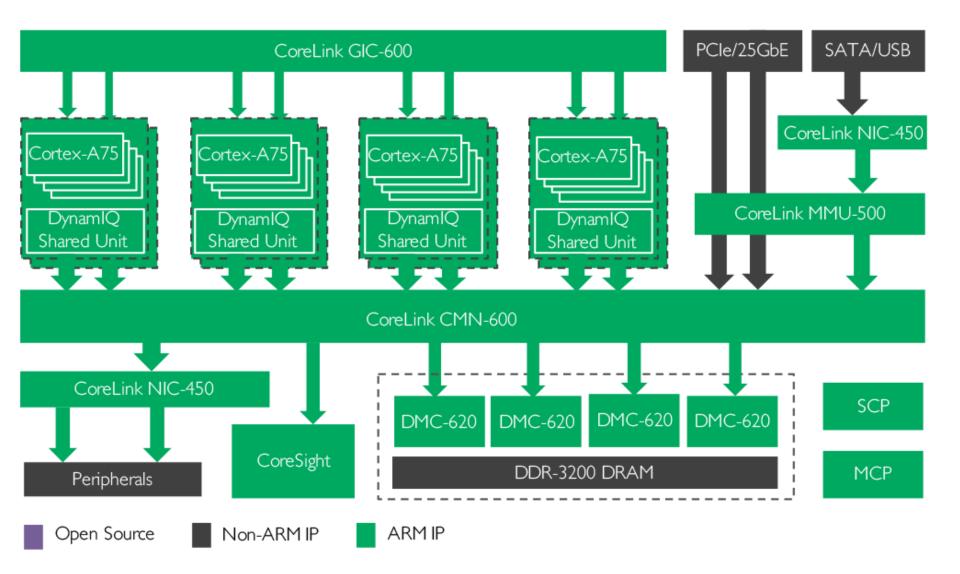

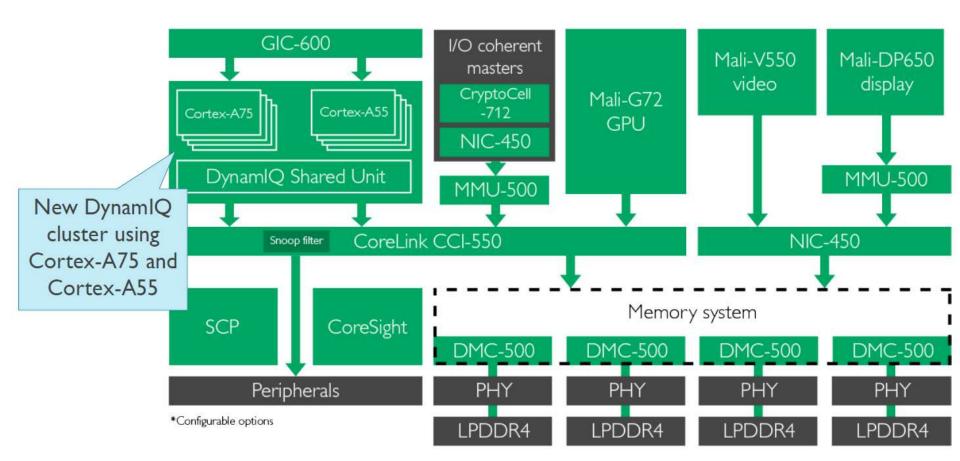

### Example: ARM's IP offer relating the Cortex-A73 processor [89]

#### Graphic IP

- ARM Mali<sup>™</sup>-G71

- Mali-DP550 (Display processor)

- Mali-V550 (Video Processor)

#### Other IP

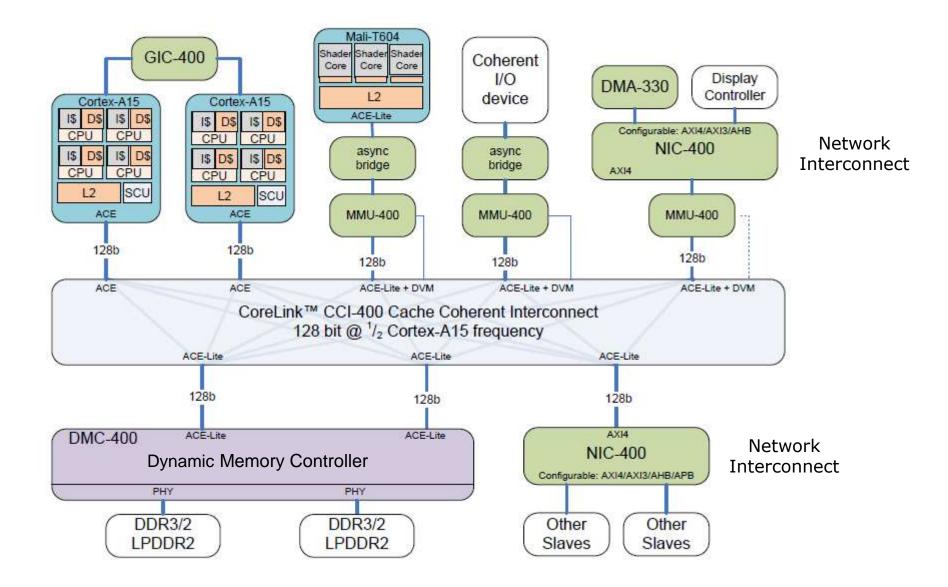

- ARM <u>CoreLink</u><sup>™</sup> CCI-550 (Cache Coherent Interconnect)

- CoreLink GIC-500 (Interrupt Controller)

- CoreLink MMU-500 (System Memory Management Unit)

- CoreLink TZC-400 (ARM TrustZone® Controller)

- CoreLink DMC-500/DMC-520 (Dynamic Memory Controller)

- ARM CoreSight<sup>™</sup> SoC-400 (Debug and Trace)

- ARM POP<sup>™</sup> (Physical IP)

#### Tools

- ARM DS-5 Development Studio

- Fixed Virtual Platforms

- ARM Versatile<sup>™</sup> Express

- ARM Compiler 6

- ARM Fast Models

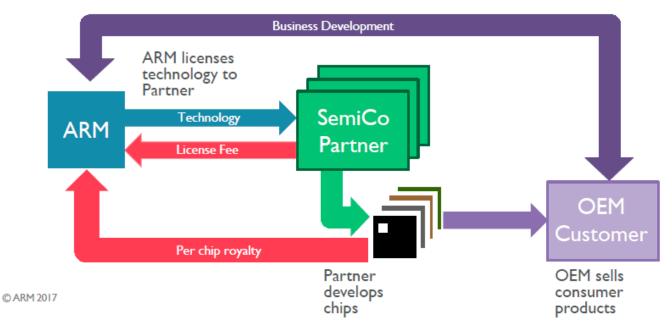

### ARM's business model [117]

6

## **ARM Business Model**

- ARM develops technology that is licensed to semiconductor companies

- ARM receives an upfront license fee and a royalty on every chip that contains its technology

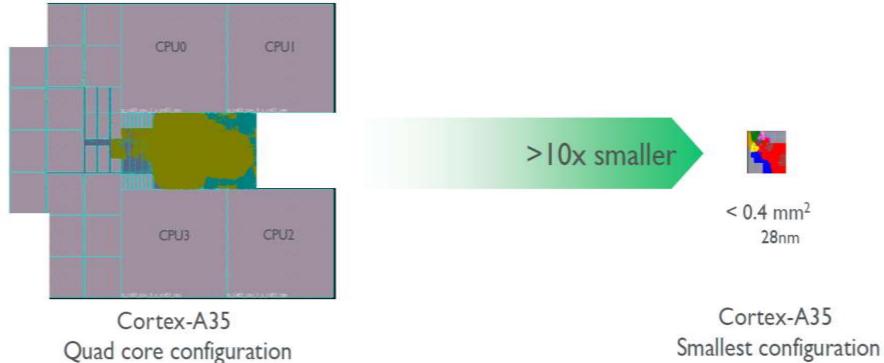

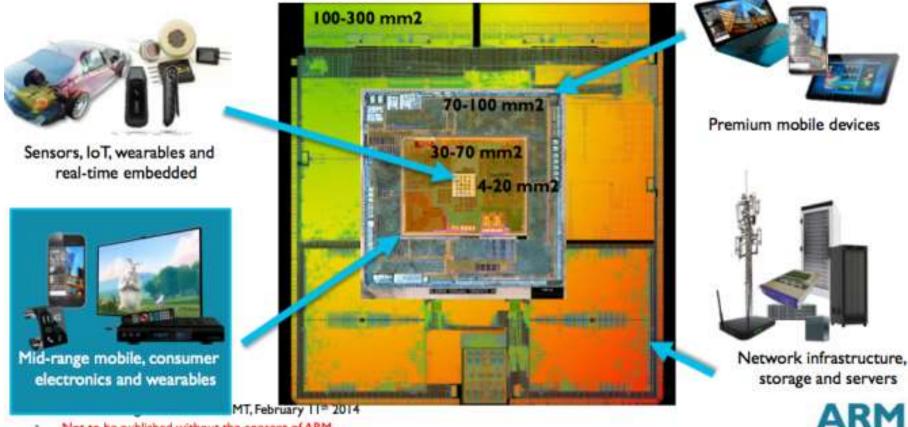

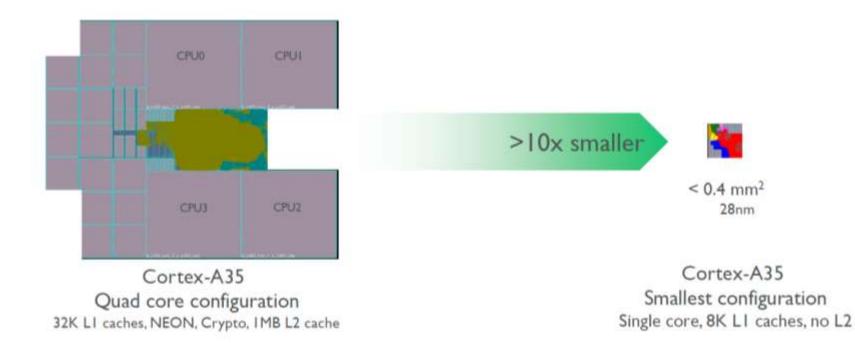

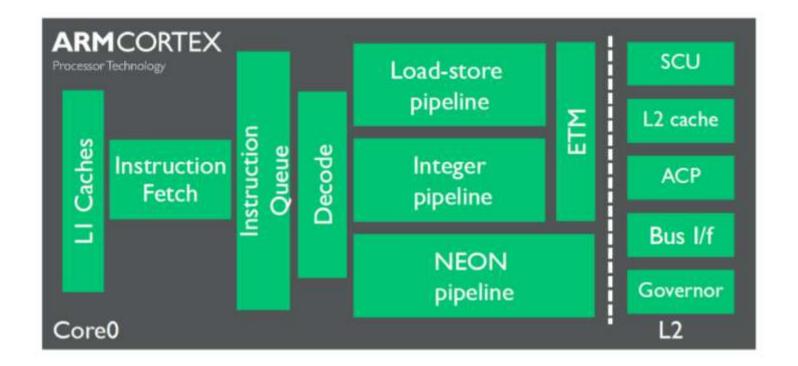

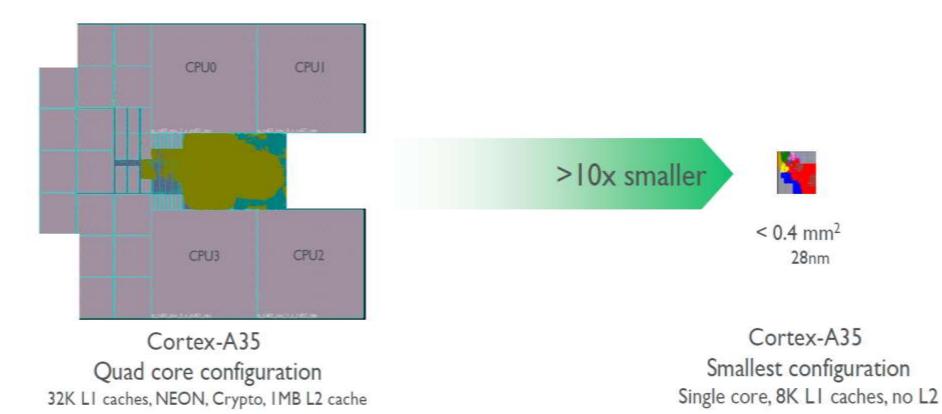

### Example for the range of configurability of a processor [90]

Configuration options of the Cortex-A35 ranging from mobile to deeply embedded

Single core, 8K L1 caches, no L2

32K LI caches, NEON, Crypto, IMB L2 cache

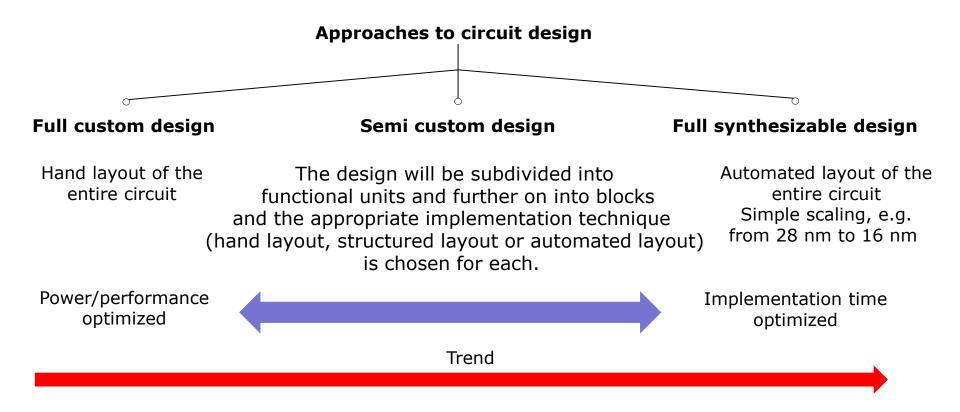

#### Evolution of the approaches used to circuit design -1 [1]

Evolution of the approaches used to circuit design -2 [1]

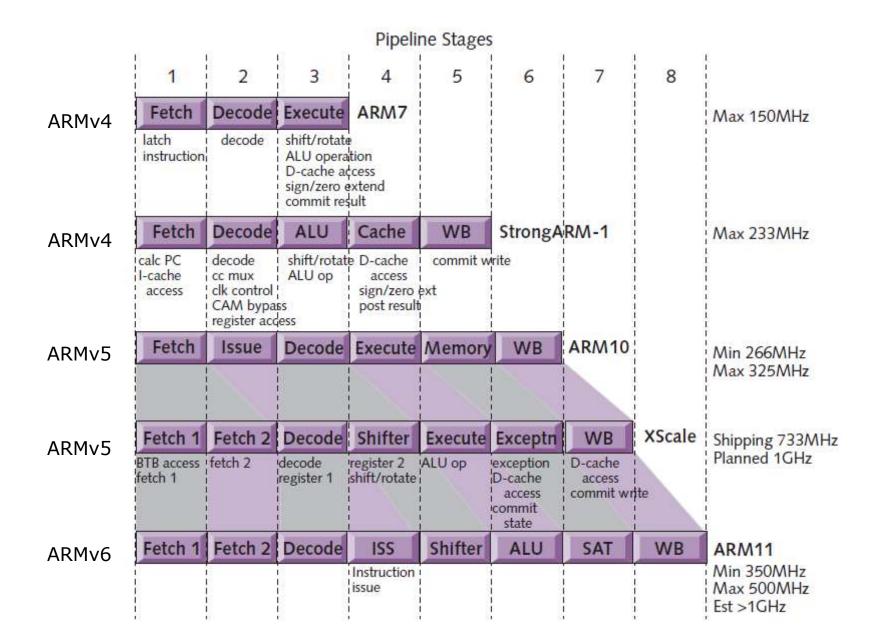

- ARM's processor designs before the Cortex-A9 were partly hand layouts and partly automated layouts.

- ARM's first fully synthesizable design was the Cortex-A9 processor (announced in 2007).

- Recently, automated design tools are typically used for processor design.

- Over time more and more advanced standard cell libraries were developed that have a large variety of design options, e.g. cell types or drive strengths, which lessens the need for custom design.

Design approaches used by Qualcomm to develop recent processors [116]

| 810                                      | 820                                     | 835                                                 |

|------------------------------------------|-----------------------------------------|-----------------------------------------------------|

| Stock ARM<br>(Full synthesizable design) | Custom                                  | Semi-Custom : Built on ARM<br>Cortex® Technology    |

| Rapid 64-bit deployment                  | High performance with<br>improved power | Higher performance with<br>extreme power efficiency |

| Limited System Integration               | Tight system integration                | Tight system integration                            |

| 4xA53 2.0+<br>4xA57 1.55                 | 2xKryo 2.15+<br>2xKryo 1.59             | 4xKryo 280 2.45+<br>4xKryo 280 1.9                  |

| 20 nm<br>(2015)                          | 14 nm<br>(2015)                         | 10 nm<br>(2016)                                     |

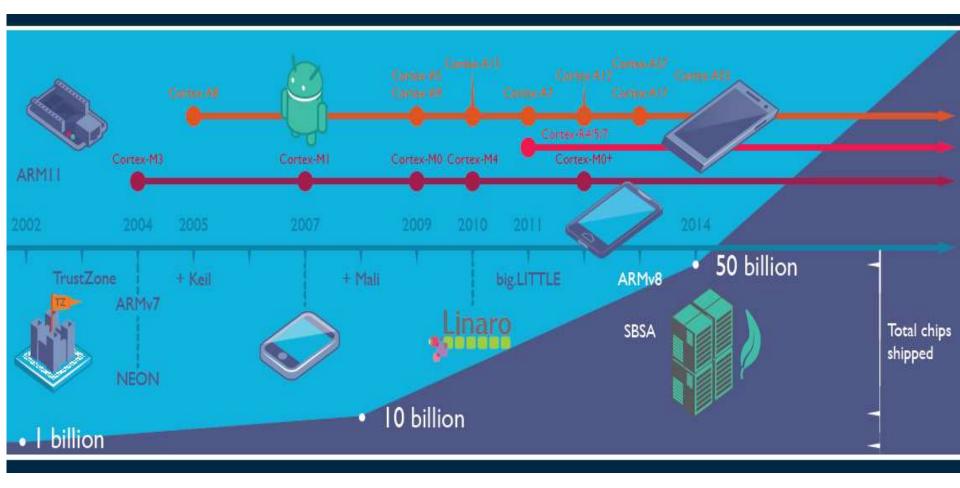

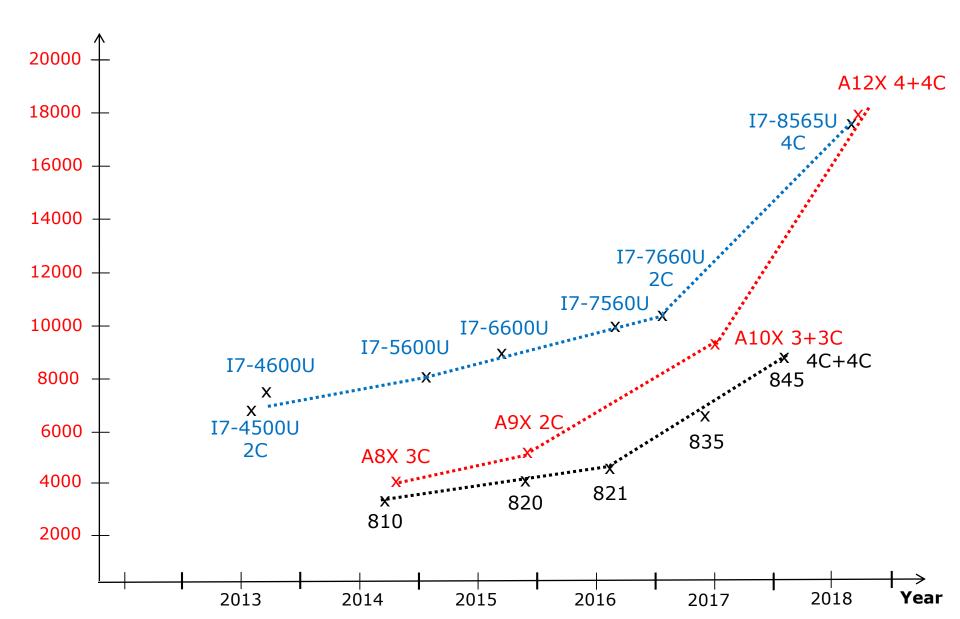

Dominance of AMD designs in the embedded and mobile market (including smartphones and tablets)

- ARM designs dominate recently the embedded and the mobile market (including smartphones and tablets).

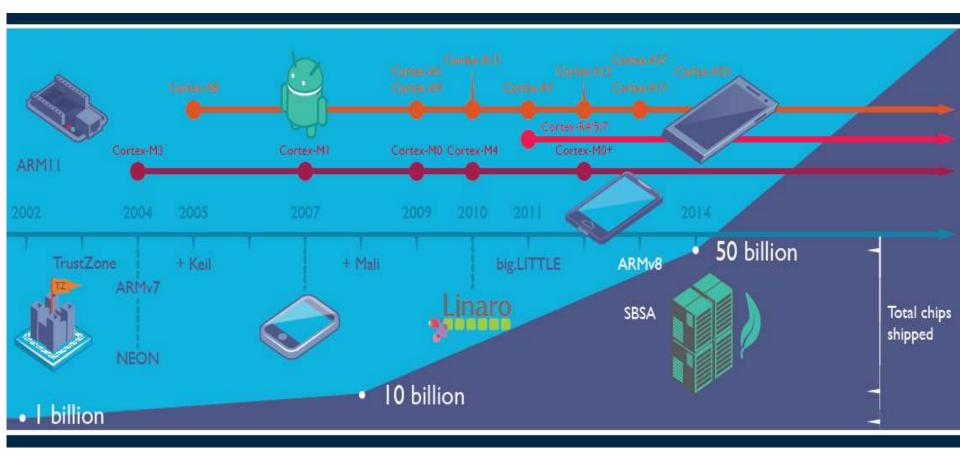

- As of 2014 more than 50 billion ARM based processors have been produced in total, up from 10 billion in 2008 [59], [19], as indicated in the next Figure.

#### 1. Evolution of ARM (9)

#### Total number of ARM based chips shipped [19]

Keil: Software development tool for embedded processors

Linaro: Nonprofit company, established by ARM, Freescale, IBM, Samsung, ST-Ericsson and TI to support open source software developers using Linux on SoCs.

SBSA: Server Base System Architecture, a standardized server platform for 64-bit ARM processors.

#### Historical remarks [60], [61] -1

- ARM's parent company is Acorn Computers (UK).

- Acorn Computers started their Acorn RISC Machine project in October 1983 (two years after the introduction of the IBM PC) to develop an own powerful processor for a line of business computers.

- The acronym ARM was coined originally at this time (1983) from the designation Acorn RISC Machine.

- In 1990 the company Advanced RISC Machines Ltd. (ARM Ltd.) was founded as a joint venture of Acorn Computers, Apple Computers and VLSI Technology.

- Accordingly, also the interpretation of ARM was changed to "Advanced RISC Machines".

#### 1. Evolution of ARM (11)

#### Historical remarks -2

Figure: The headquarters of ARM Ltd. about 1990 [62]

Historical remarks -3

Finally, in 1998 the company went to the stock exchange and its name was changed to ARM Holdings plc, to its current designation.

#### 1. Evolution of ARM (13)

Historical remarks -4

Figure: ARM's recent headquarter in Cambridge (UK) [78]

#### Acquisition of ARM by Softbank (Japan)

- Announced in 07/2016

- Completed in 09/2016

- Price: 31 bUSD (ARM's revenues in 2015  $\approx$  1.5 bUSD)

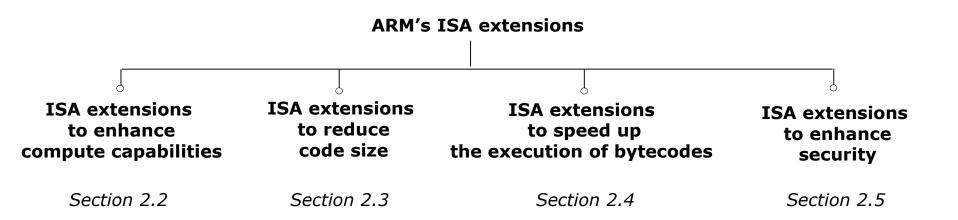

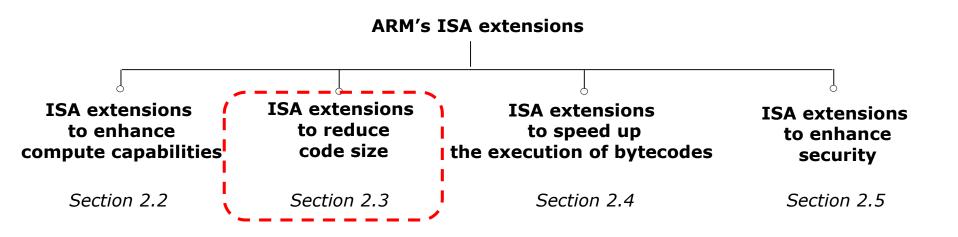

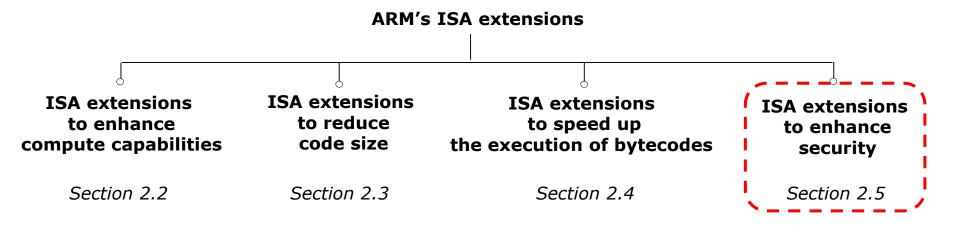

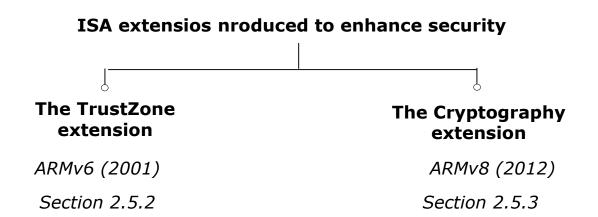

#### 2. Evolution of the ARM ISA

- 2.1 Overview

- 2.2 ISA extensions introduced to enhance compute capabilities

- 2.3 ISA extensions introduced to reduce the code size

- 2.4 ISA extensions introduced to enhance security

(Only Section 2.1 and 2.2.1 will be discussed)

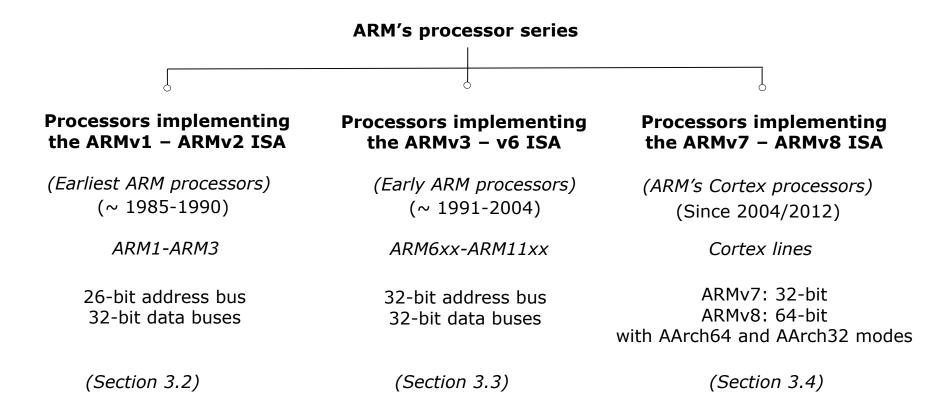

### 2.1 Overview

#### 2.1 Overview

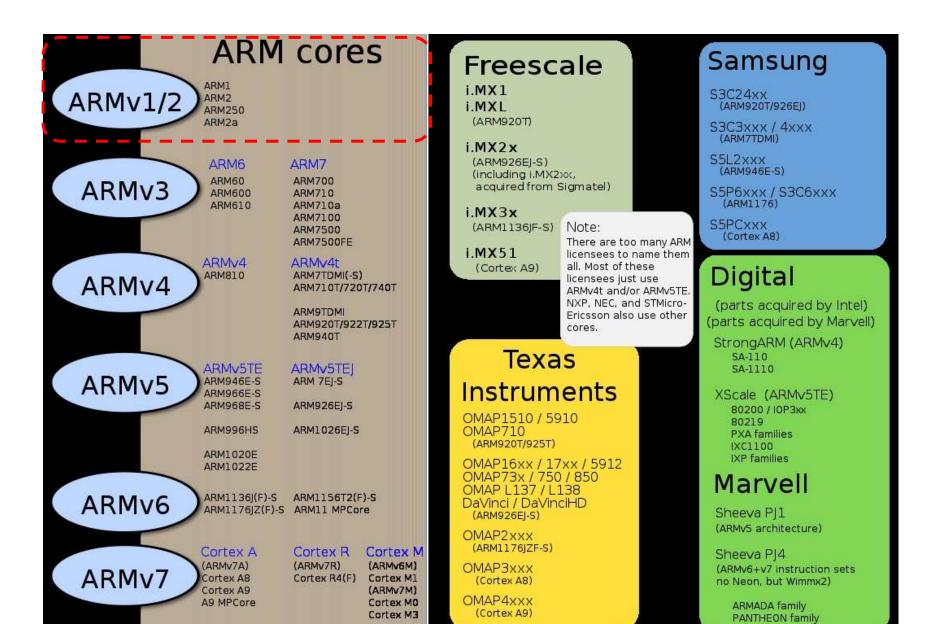

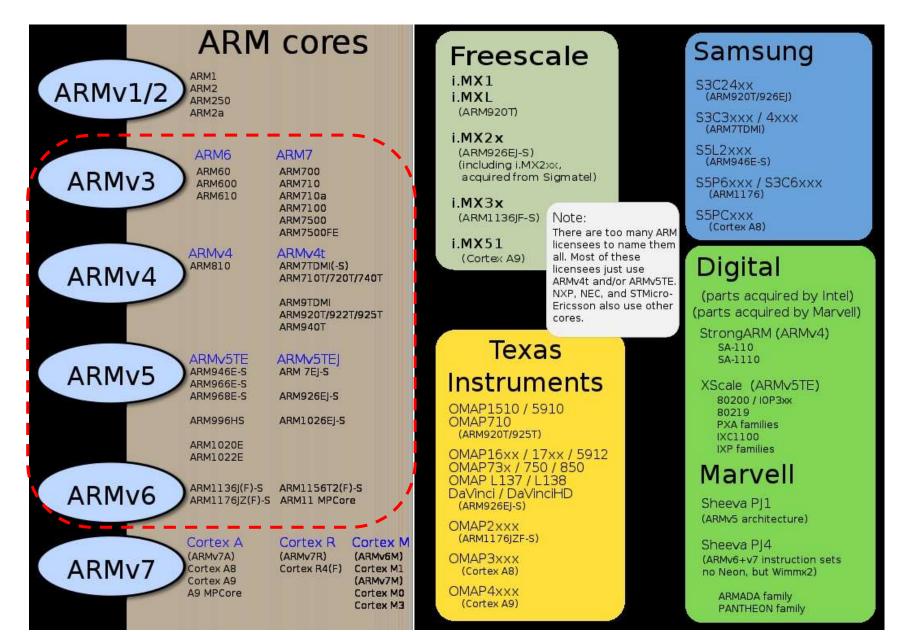

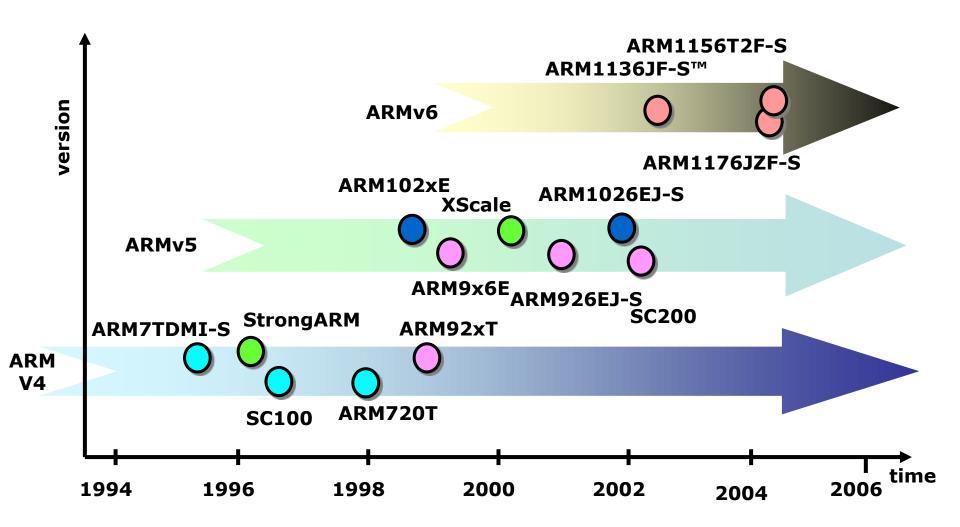

- There are eight ARM ISA versions, designated as ARMv1 to ARMv8. These are described in the related Architecture Reference Manuals.

- The earliest versions (ARMv1 and ARMv2) provided an address range of only 26 bits, the first ISA version with 32 bit address range was the ARMv3.

- Accordingly, we consider the ISA version ARMv3 as ARM's basic ISA and discuss its evolution subsequently.

## Example: Half page of the ARMv8 Architecture Reference Manual [] (1/2 from 6354)

#### C7.2.332 UQSHL (register)

Unsigned saturating Shift Left (register). This instruction takes each element in the vector of the first source SIMD&FP register, shifts the element by a value from the least significant byte of the corresponding element of the second source SIMD&FP register, places the results in a vector, and writes the vector to the destination SIMD&FP register.

If the shift value is positive, the operation is a left shift. Otherwise, it is a right shift. The results are truncated. For rounded results, see UQRSHL.

If overflow occurs with any of the results, those results are saturated. If saturation occurs, the cumulative saturation bit FPSR.QC is set.

Depending on the settings in the CPACR EL1, CPTR EL2, and CPTR EL3 registers, and the current Security state and Exception level, an attempt to execute the instruction might be trapped.

#### Scalar

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 22 | 21 | 20 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 |    | 5 | 4  | 0 |

|----|----|----|----|----|----|----|----|-------|----|----|----|----|----|----|----|----|----|---|----|---|----|---|

| 0  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | size  | 1  | Rm |    | 0  | 1  | 0  | 0  | 1  | 1  |   | Rn |   | Rd |   |

|    |    | U  |    |    |    |    |    |       |    |    |    |    |    |    | R  | S  |    |   |    |   |    |   |

#### Scalar variant

UQSHL  $\langle V \rangle \langle d \rangle$ ,  $\langle V \rangle \langle n \rangle$ ,  $\langle V \rangle \langle m \rangle$

#### Decode for this encoding

```

integer d = UInt(Rd);

integer n = UInt(Rn);

integer m = UInt(Rm);

integer esize = 8 << UInt(size);</pre>

```

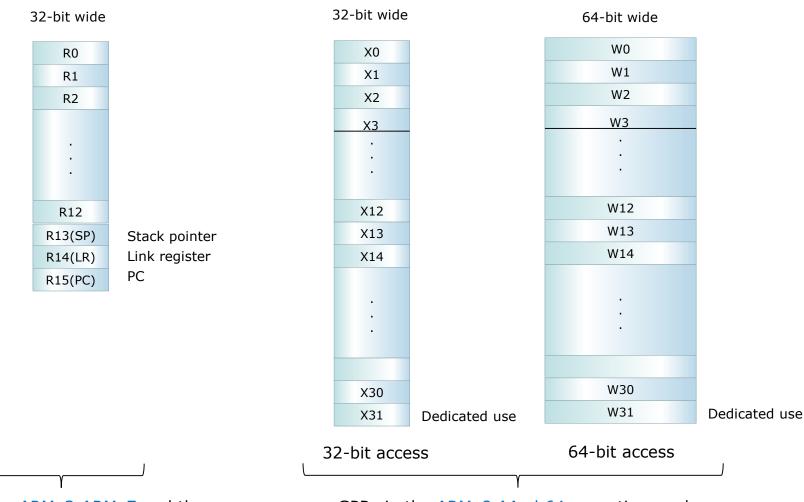

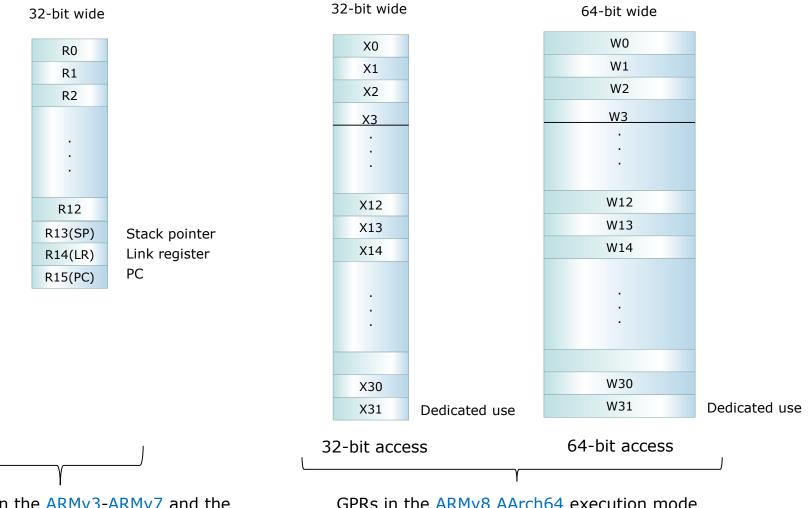

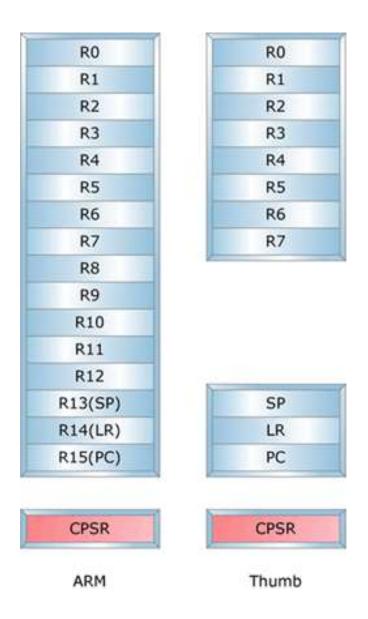

Key features of ARM's basic ISA

- It is a 32-bit RISC ISA capable to process basically 32-bit scalar FX or logical data.

- The ISA has 16 32-bit registers, called the core registers.

- 13 out of them are used as general purpose registers (GPRs), the remaining three are dedicated registers, as shown below.

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| RO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

| R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

| R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

| R3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

| R4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

| R5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

| R6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

| R7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

| R8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

| R9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

| R10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| R11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| R12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| R13(SP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Stack pointer |

| R14(LR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Link register |

| R15(PC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PC            |

| and the second sec |               |

Figure: The core registers of the ARM ISA (in the ISA versions ARMv3-ARMv7) [63]

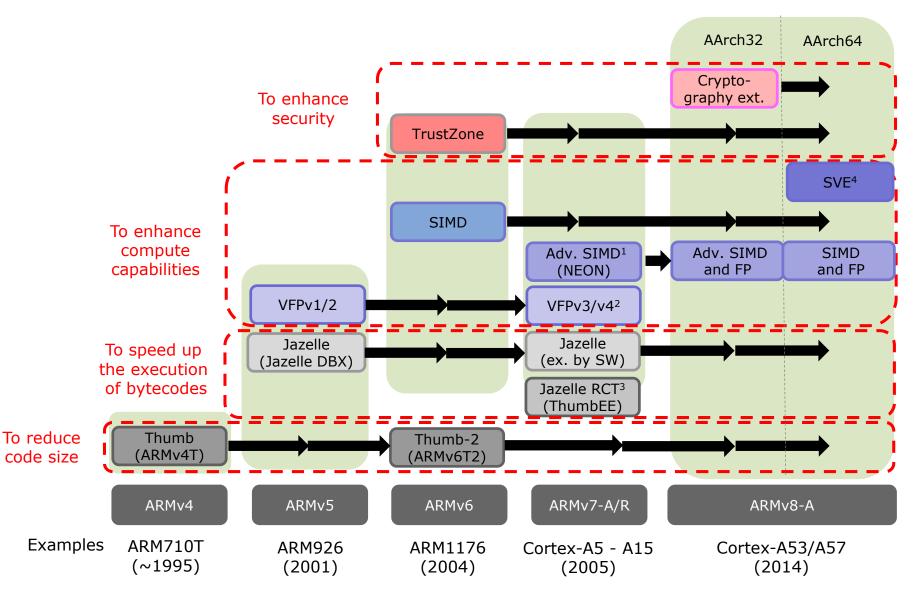

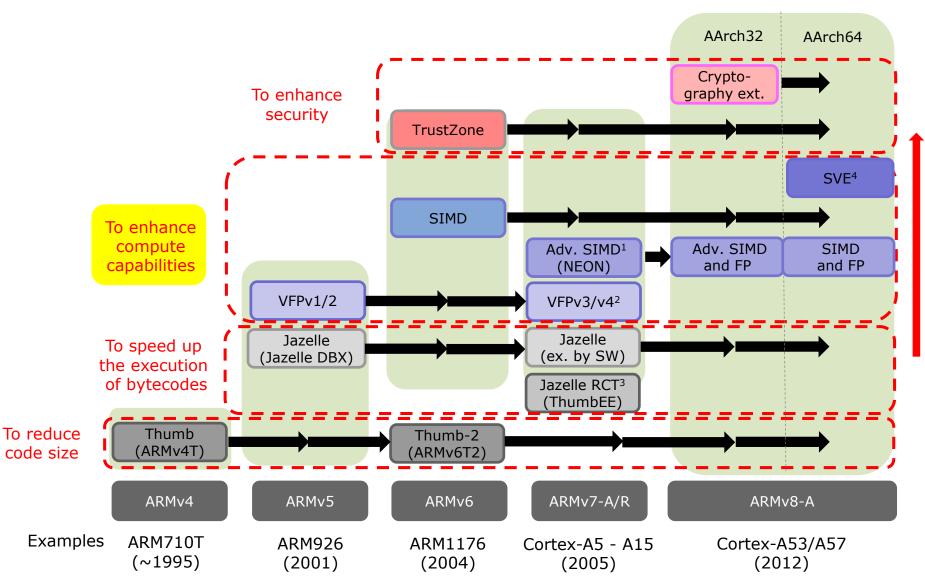

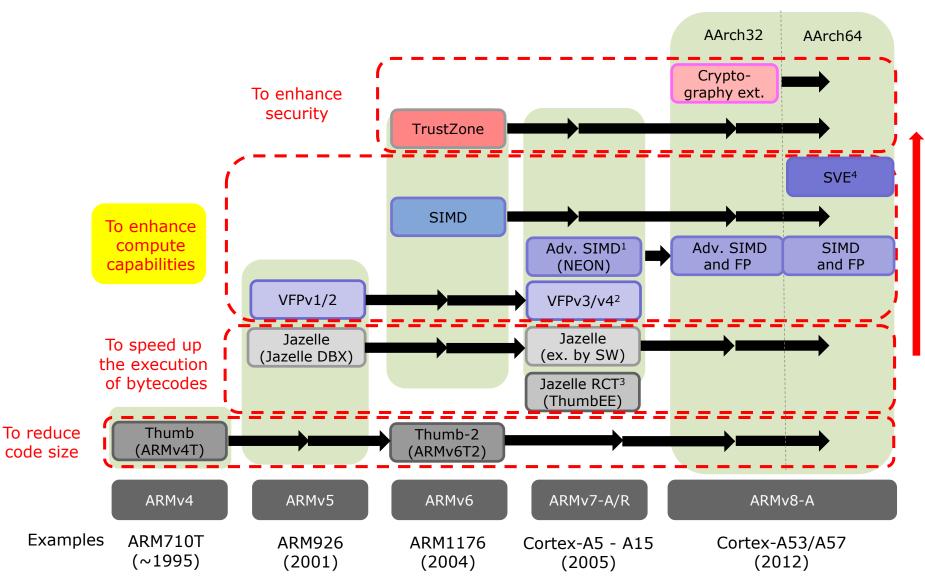

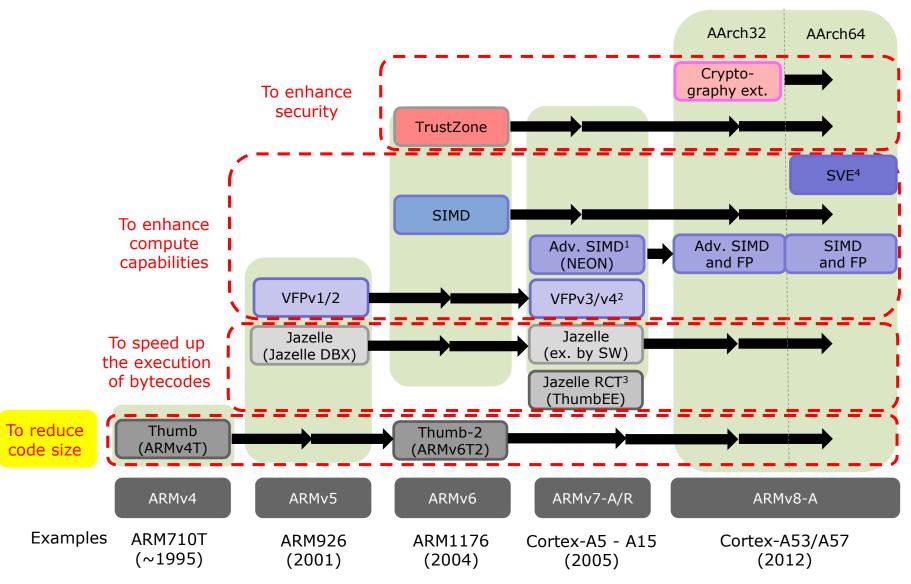

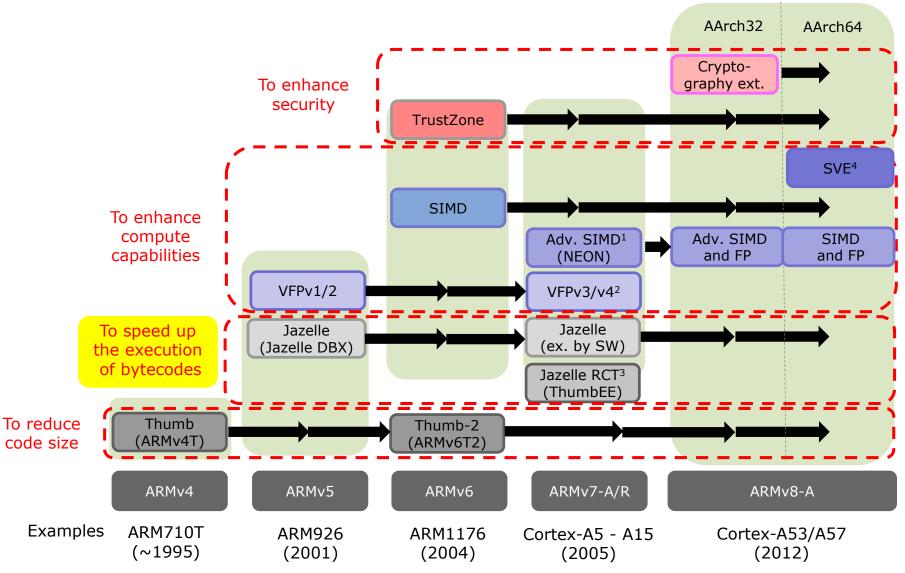

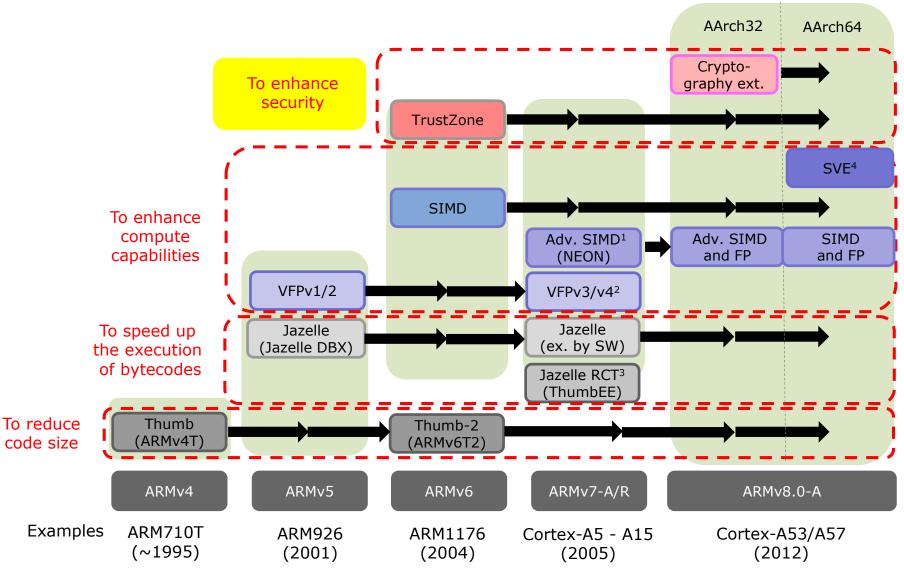

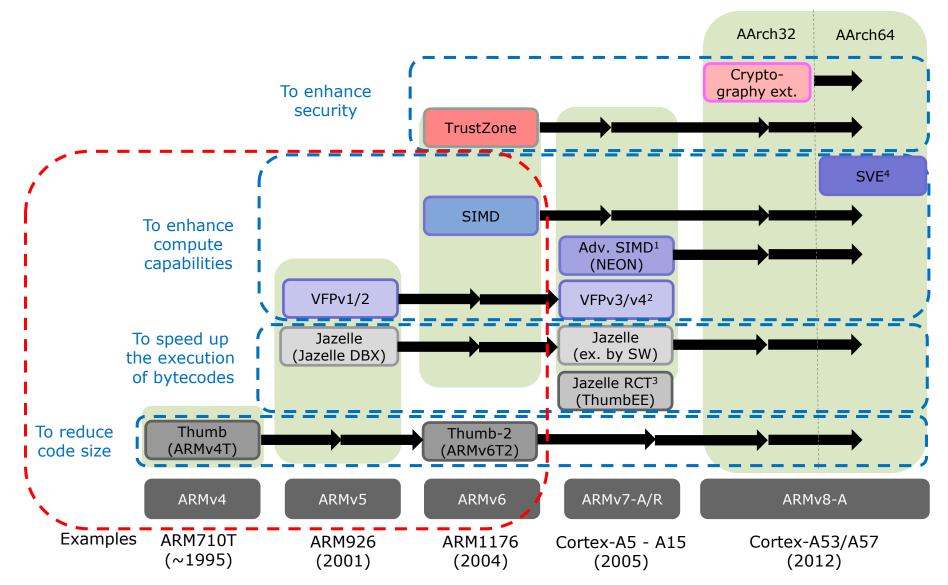

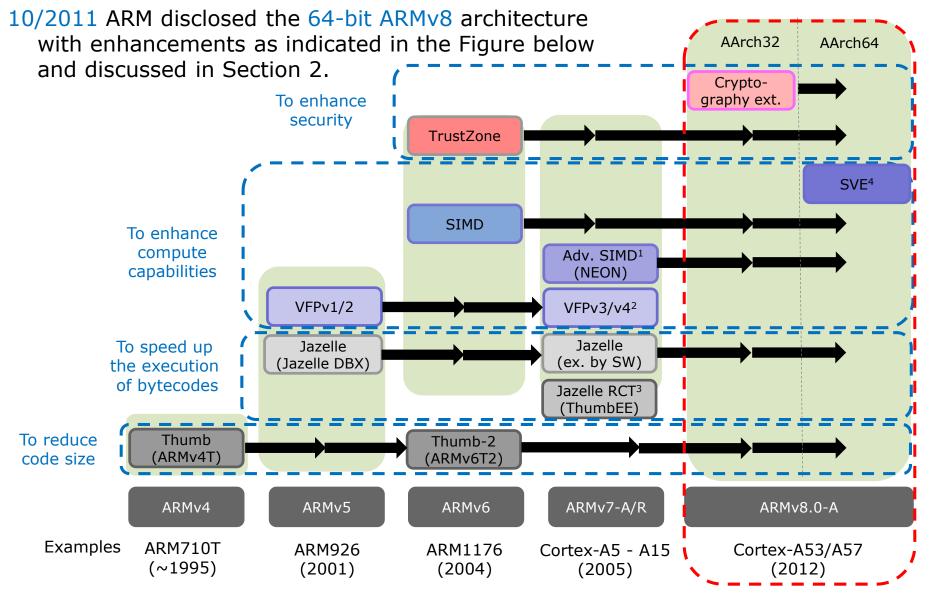

Main extensions introduced in ARM's basic ISA (simplified) -1

Main extensions introduced in ARM's basic ISA (simplified) -2 (Based on [64])

Remarks: See on the next slide.

#### Remarks

<sup>1</sup>The Advanced SIMD architecture extension is commonly referred to as the NEON technology.

The VFP subset became depricated in the ARMv8 ISA.

<sup>3</sup>Jazelle-RTC (ThumbEE) became depricated in ARMv7 Issue C in 10/2011.

<sup>4</sup>The SVE (Scalable Vector Extension) subset became introduced in the ARMv8 ISA only in 2016.

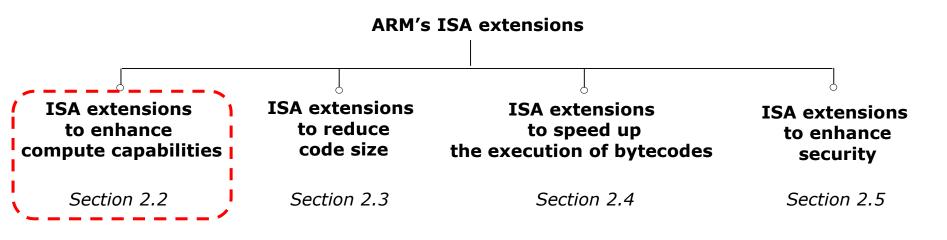

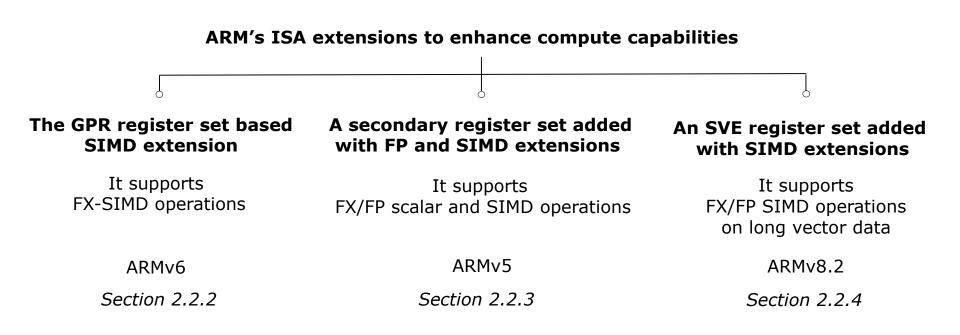

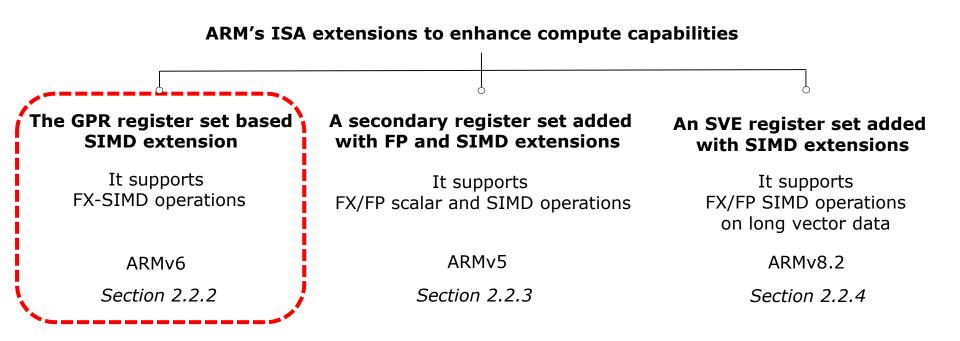

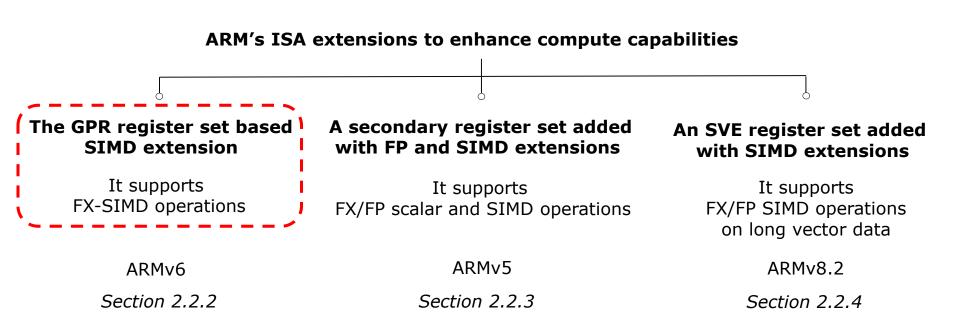

#### 2.2 ISA extensions introduced to enhance compute capabilities

- 2.2.1 Overview

- 2.2.2 The GPR register set based SIMD extension

- 2.2.3 Secondary register set based VFP and NEON extensions

- 2.2.4 The SVE register set based SVE extension

Only Section 2.2.1 will be discussed.

### 2.2.1 Overview

#### 2.2.1 Overview (1)

2.2 ISA extensions introduced to enhance compute capabilities2.2.1 Overview

Overview of the ISA extensions introduced to enhance compute capabilities

Remarks: See on the slide 2.1 Overview (5).

#### ISA extensions introduced to enhance compute capabilities

#### ISA extensions introduced to enhance compute capabilities

#### ISA extensions introduced to enhance compute capabilities (until 2012)

| ARM ISA |      | Name of                            | Basic arch. |              | GPR-based                         | Secondary register set based extensions |                                          |                                                                                    |  |  |  |

|---------|------|------------------------------------|-------------|--------------|-----------------------------------|-----------------------------------------|------------------------------------------|------------------------------------------------------------------------------------|--|--|--|

| Name    |      | the<br>extensions                  | GPRs        | Data<br>type | FX-SIMD<br>data type<br>extension | Available<br>reg. set                   | Scalar<br>data types                     | Vector<br>data types                                                               |  |  |  |

| ARMv1   | 1985 |                                    | n.a.        |              |                                   |                                         |                                          |                                                                                    |  |  |  |

| ARMv2   | 1989 |                                    | n.a.        |              |                                   |                                         |                                          |                                                                                    |  |  |  |

| ARMv3   | 1991 |                                    |             |              |                                   |                                         |                                          |                                                                                    |  |  |  |

| ARMv4   | 1996 |                                    |             |              |                                   |                                         |                                          |                                                                                    |  |  |  |

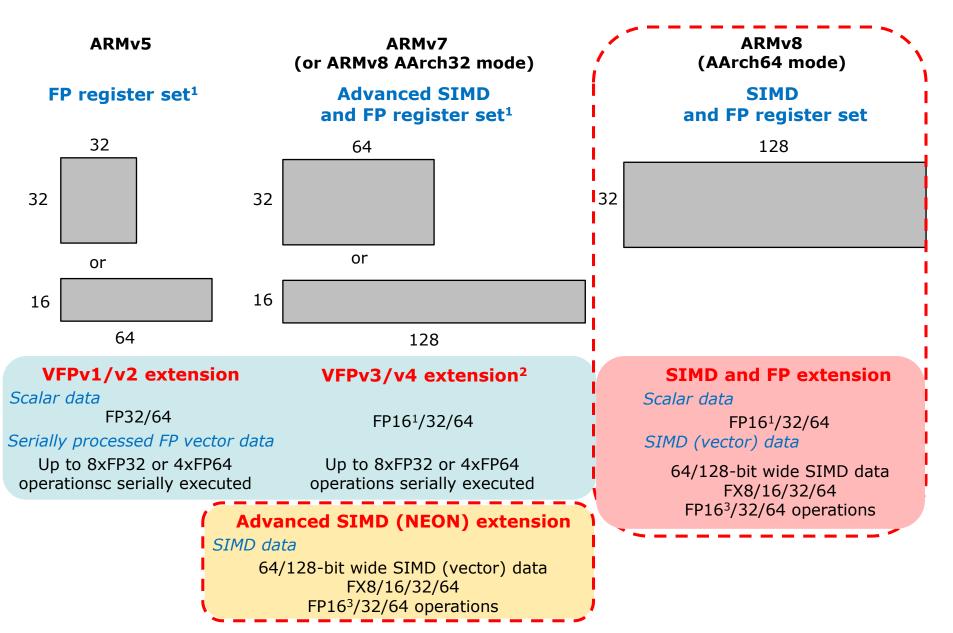

| ARMv5   | Year | VFP(v1) <sup>1</sup>               |             |              |                                   | FP register set                         | FP 32/64                                 | FP 32/64                                                                           |  |  |  |

|         |      | VFP2 <sup>1</sup>                  |             |              |                                   | 32x32/16x64                             |                                          | Serially ex.                                                                       |  |  |  |

| ARMv6   |      | SIMD                               |             | FX32         | 32-bit wide<br>FX8/16             |                                         |                                          |                                                                                    |  |  |  |

|         |      | VFPv3 <sup>2</sup>                 | 13x32       |              |                                   | Adv. SIMD and<br>FP register set        | +FP 164                                  | FP 16 <sup>4</sup> /32/64                                                          |  |  |  |

| ARMv7   | 2005 | VFPv4 <sup>2,3,4</sup>             |             |              |                                   | 32x64 or<br>16X128                      | + FMA                                    | Serially<br>executed                                                               |  |  |  |

|         | 2005 | Adv. SIMD<br>(NEON) <sup>4,5</sup> |             |              |                                   | 32x64<br>or16x128                       |                                          | 64/128-bit wide<br>FX 8/16/32/64<br>FP 16 <sup>5</sup> /32/64<br>+FMA <sup>5</sup> |  |  |  |

| ARMv8   |      | AArch32                            |             | 5.(22        | 32-bit wide<br>FX8/16             | 32x64 or<br>16x128                      | FP<br>16 <sup>4</sup> /32/64             | As for ARMv7<br>Adv. SIMD                                                          |  |  |  |

|         | 2012 | AArch64                            | 31x64       | FX32<br>/64  | 32/64-bit<br>wide<br>FX8/16/32    | SIMD and FP<br>register set<br>32x128   | FX 8//64<br>FP<br>16 <sup>4</sup> /32/64 | As for ARMv7<br>Adv. SIMD                                                          |  |  |  |

#### Remarks

<sup>1</sup>VFPv2 vs. VFP(v1): VFPv2 adds some enhancements and modifications to VFPv1

<sup>2</sup>VFPv3/v4 and advanced SIMD register space:

Certain processors implement only 16 64-bit wide registers with the option to use this register space as 32 32-wide registers.

<sup>3</sup>VFP4 is implemented on certain ARMv7 processors.

It adds FMA (Fused Multiply Accumulate) instructons to the VFPv3 instructon set.

<sup>4</sup>FP16 supports only data conversion between FP16 and FP32/FP64.

<sup>5</sup>In the Advanced SIMD (NEON) extension FP16 is supported only if VFP3/VFP4 is implemented respectively, FMA if VFP4 is implemented.

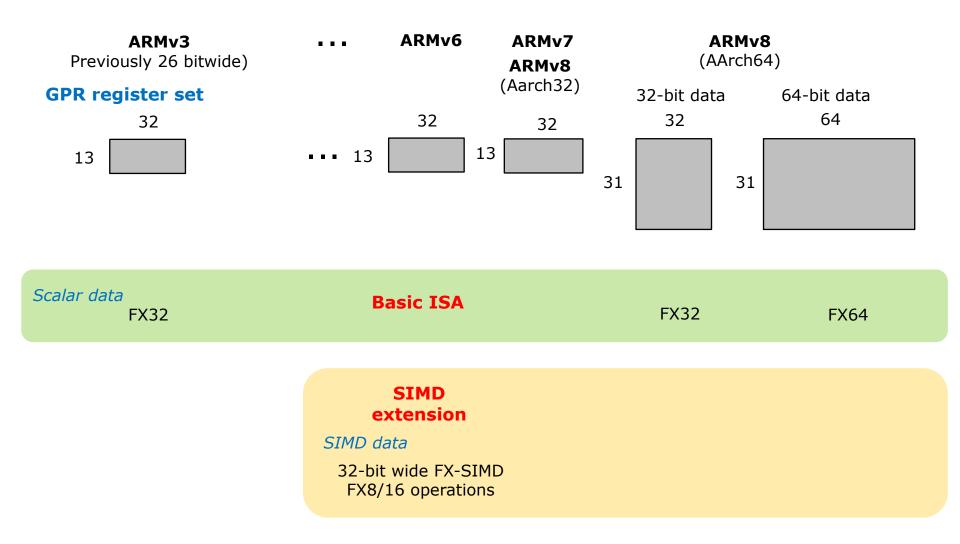

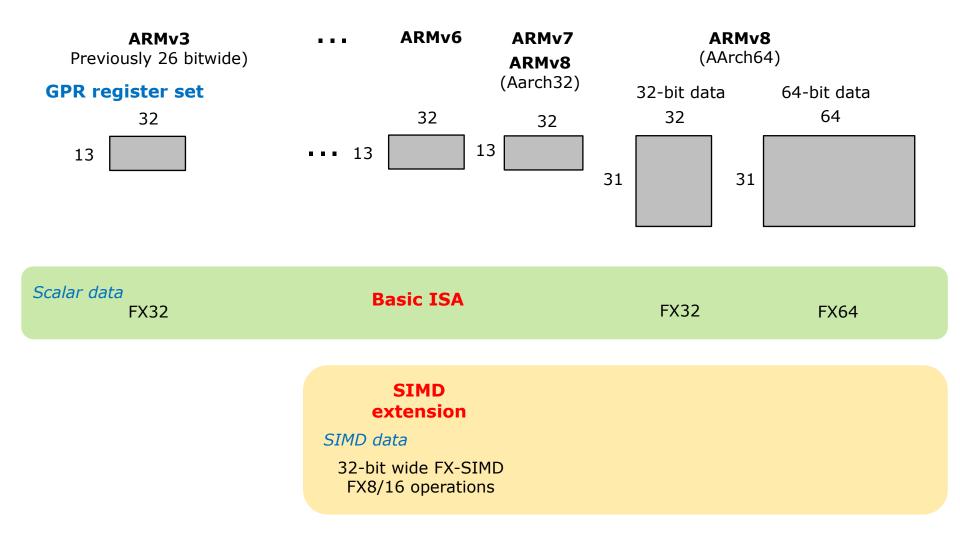

The GPR register set based SIMD extension introduced in the ARMv6 ISA

#### 2.2.1 Overview (8)

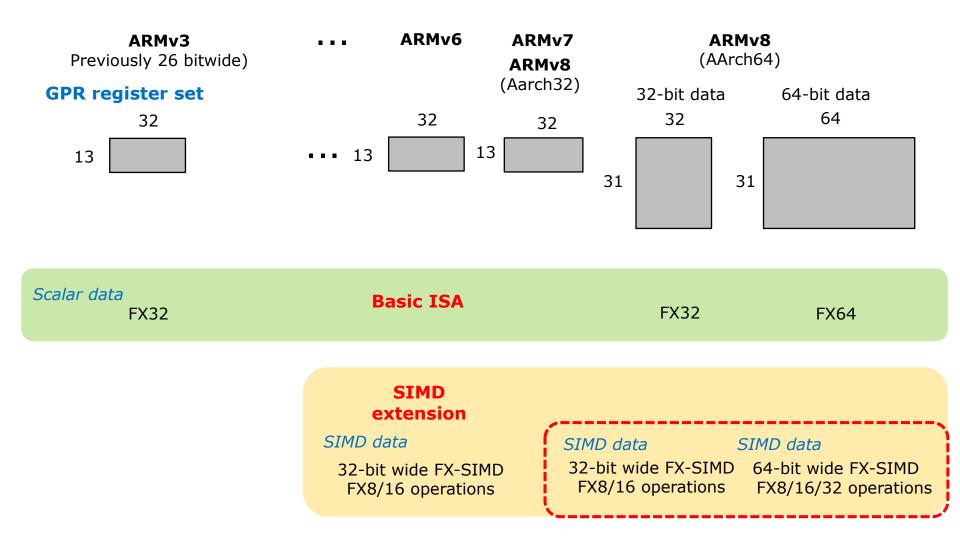

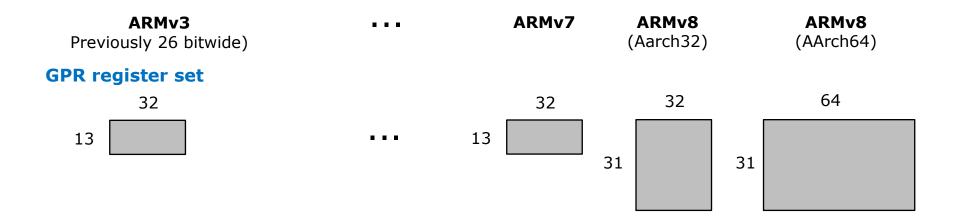

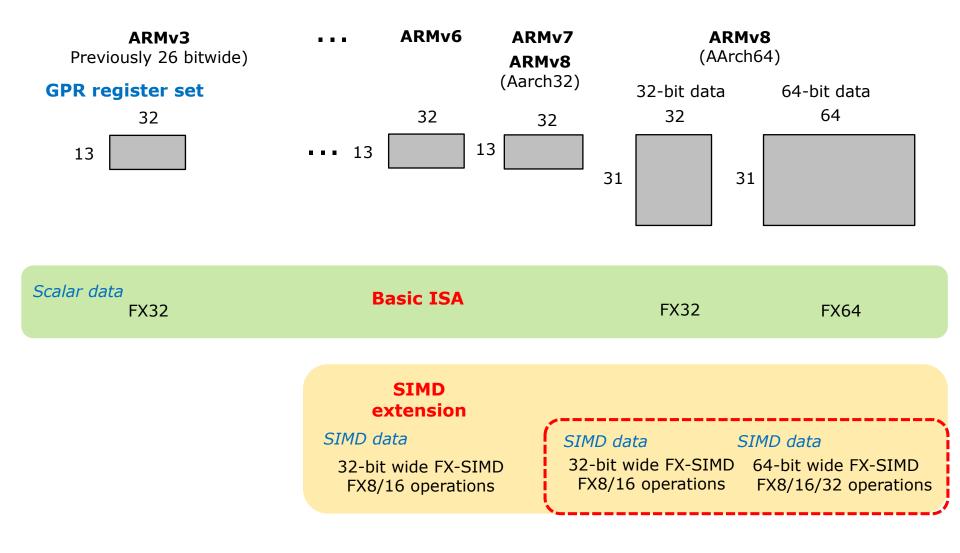

Extension of the GPR register set available in the ARMv8 ISA 63], [66] The ARMv8 ISA expanded the number of GPRs as seen in the Figure below.

GPRs in the ARMv3-ARMv7 and the ARMv8 AArch32 execution mode

GPRs in the ARMv8 AArch64 execution mode

The GPR register set based SIMD extension introduced in the ARMv8 ISA

## Secondary register set based FP and SIMD extensions -1

# 2.2.1 Overview (10)

# Secondary register set based FP and SIMD extensions -2

| ARM ISA |      | Name of Basic a                    |       |              |                                   | Secondary register set based extensions |                                          |                                                                                                                                         |  |  |  |  |  |  |

|---------|------|------------------------------------|-------|--------------|-----------------------------------|-----------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Name    |      | the<br>extensions                  | GPRs  | Data<br>type | FX-SIMD<br>data type<br>extension | Available<br>reg. set                   | Scalar<br>data types                     | Vector<br>data types                                                                                                                    |  |  |  |  |  |  |

| ARMv1   | 1985 |                                    | n.a.  |              |                                   |                                         |                                          | 1                                                                                                                                       |  |  |  |  |  |  |

| ARMv2   | 1989 |                                    | n.a.  |              |                                   |                                         |                                          |                                                                                                                                         |  |  |  |  |  |  |

| ARMv3   | 1991 |                                    |       |              |                                   |                                         |                                          |                                                                                                                                         |  |  |  |  |  |  |

| ARMv4   | 1996 |                                    |       |              |                                   |                                         |                                          | 1                                                                                                                                       |  |  |  |  |  |  |

| ARMv5   | Year | VFP(v1) <sup>1</sup>               |       |              |                                   | FP register set                         | FP 32/64                                 | FP 32/64<br>Serially ex.                                                                                                                |  |  |  |  |  |  |

|         | Tear | VFP2 <sup>1</sup>                  |       |              |                                   | 32x32/16x64                             | TF 52/04                                 |                                                                                                                                         |  |  |  |  |  |  |

| ARMv6   |      | SIMD                               |       |              | 32-bit wide<br>FX8/16             |                                         |                                          | 1<br>1<br>1                                                                                                                             |  |  |  |  |  |  |

| ARMv7   |      | VFPv3 <sup>2</sup>                 | 13x32 | FX32         |                                   | Adv. SIMD and<br>FP register set        | +FP 16 <sup>4</sup>                      | FP 16 <sup>4</sup> /32/64<br>Serially<br>executed<br>64/128-bit wide<br>FX 8/16/32/64<br>FP 16 <sup>5</sup> /32/64<br>+FMA <sup>5</sup> |  |  |  |  |  |  |

|         | 2005 | VFPv4 <sup>2,3,4</sup>             |       |              |                                   | 32x64 or<br>16X128                      | + FMA                                    |                                                                                                                                         |  |  |  |  |  |  |

|         | 2003 | Adv. SIMD<br>(NEON) <sup>4,5</sup> |       |              |                                   | 32x64<br>or16x128                       |                                          |                                                                                                                                         |  |  |  |  |  |  |

|         |      | AArch32                            |       |              | 32-bit wide<br>FX8/16             | 32x64 or<br>16x128                      | FP<br>16 <sup>4</sup> /32/64             | As for ARMv7<br>Adv. SIMD                                                                                                               |  |  |  |  |  |  |

| ARMv8   | 2012 | AArch64                            | 31x64 | FX32<br>/64  | 64-bit wide<br>FX8/16/32          | SIMD and FP<br>register set<br>32x128   | FX 8//64<br>FP<br>16 <sup>4</sup> /32/64 | As for ARMv7<br>Adv. SIMD                                                                                                               |  |  |  |  |  |  |

### Evolution of the secondary register set

## Secondary register set based FP and SIMD extensions -3

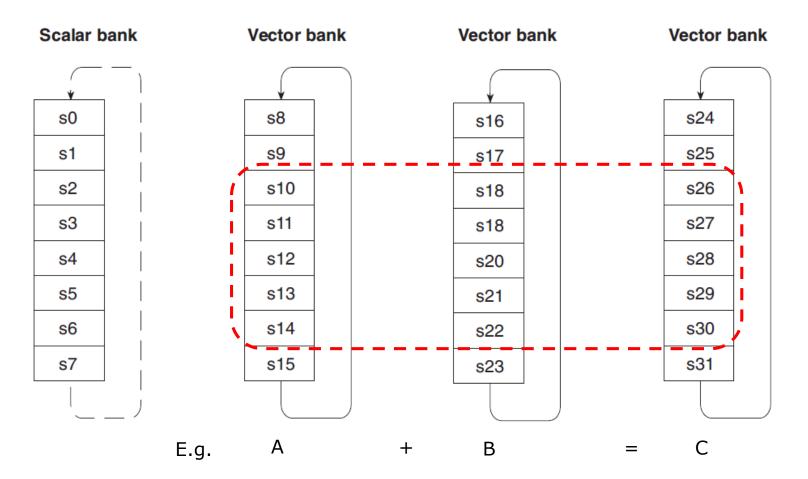

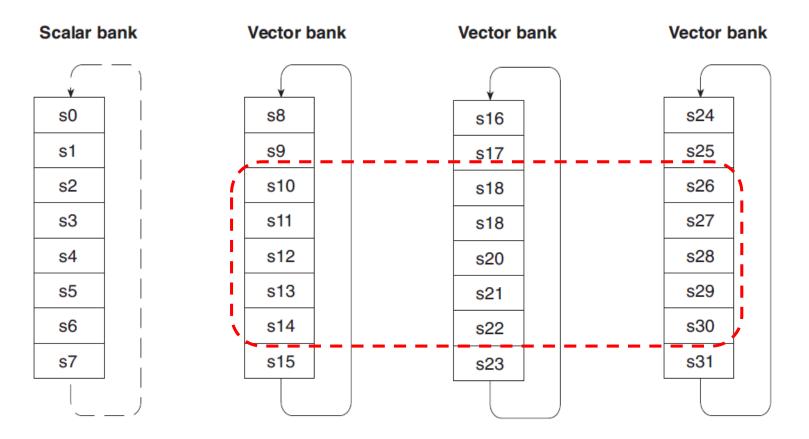

# Example: Serially processed 5-element vector operation [65]

- In the example the input operands are taken from the registers s10...s14 and s18...s22, and the result is written into the registers s26...s30.

- The execution is sequential (like a hardware implemented subroutine).

#### Secondary register set based FP and SIMD extensions -3

#### Secondary register set based FP and SIMD extensions -3

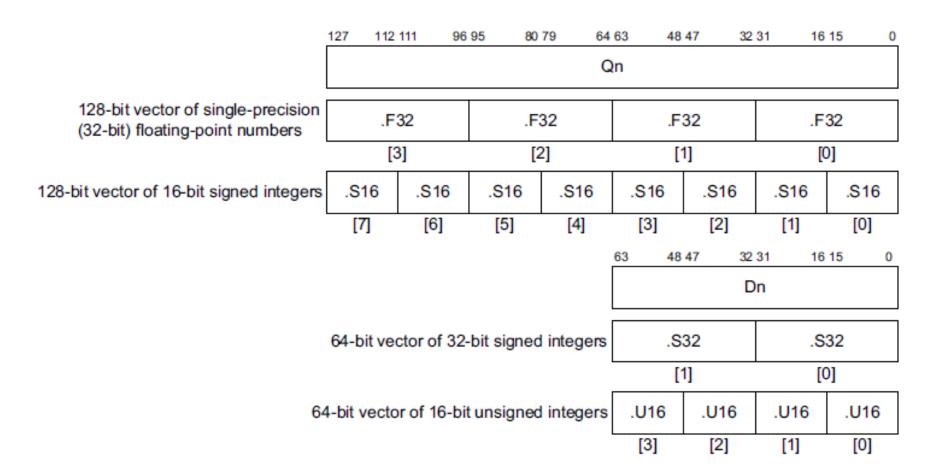

Example vector data formats of the Advanced SIMD (NEON) extension [86]

#### Secondary register set based FP and SIMD extensions -3

### The SVE register set based SIMD extension -1

# The SVE register set based SIMD extension -2

| ARM I   | SA   | Name of the | The SVE register set based SIMD extension                   |                      |                                                                         |  |  |  |  |  |

|---------|------|-------------|-------------------------------------------------------------|----------------------|-------------------------------------------------------------------------|--|--|--|--|--|

| Name    | Year | extensions  | Available<br>register set                                   | Scalar<br>data types | Vector<br>data types                                                    |  |  |  |  |  |

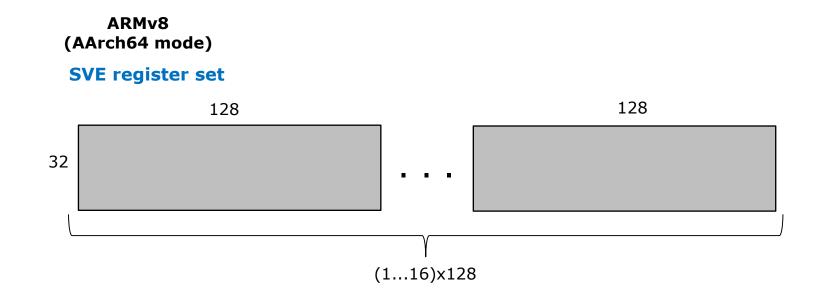

| ARMv8.2 | 2016 | SVE         | SVE register set<br>32 registers each<br>(116)x128-bit wide |                      | FX 8/16/32/64/128<br>FP 16/32/64<br>(116)x128-bit wide<br>FMA available |  |  |  |  |  |

# The SVE register set based SIMD extension -3

ARMv8.2 (AArch64 mode)

#### **SVE register set**

Up to 16 x 128-bit (Up to 2048-bit)

#### **SVE** extension

SIMD (vector) data

Up to 16 x128-bit wide SIMD data FX8/16/32/64 FP16 $^3$ /32/64 operations

# 2.2.1 Overview (17)

| Data types assuming 256-bit long<br>SVE registers [116] | 255 192 191 128 127 64 63 0<br>Zn |    |      |     |    |              |              |              |              |                         |              |                         |              |                     |                         |

|---------------------------------------------------------|-----------------------------------|----|------|-----|----|--------------|--------------|--------------|--------------|-------------------------|--------------|-------------------------|--------------|---------------------|-------------------------|

| 256-bit vector of 128-bit elements                      | .Q<br>[1]                         |    |      |     |    |              |              | .Q<br>[0]    |              |                         |              |                         |              |                     |                         |

| 256-bit vector of 64-bit elements                       | .D .D                             |    |      |     |    |              | .D           |              |              |                         | .D           |                         |              |                     |                         |

|                                                         | [3]                               |    |      | [2] |    | 1            |              |              |              | [1]                     |              | 0]                      |              | ין<br>ריין          |                         |

| 256-bit vector of 32-bit elements                       |                                   |    | .S   | .S  |    | .S           |              | .S           |              | .S                      |              | . <mark>S</mark>        |              | .S                  |                         |

|                                                         | [7]                               |    | [6]  | [5] |    | [4]          |              | [3]          |              | [2]                     |              | [1]                     |              | [0]                 |                         |

| 256-bit vector of 16-bit elements                       | .Н. Н.                            | .Н | н. н | .н  | .Н | .н           | .Н           | .н           | .н           | .н                      | .н           | .н                      | .н           | .н                  | .н                      |

| 256-bit vector of 8-bit elements                        | [15] [14]<br>.B .B .B .E<br>[31]  |    |      |     |    | [9]<br>.B .B | [8]<br>.в .в | [7]<br>.B .B | [6]<br>.B .B | <b>[5]</b><br>.в .в     | [4]<br>.в .в | [3]<br>.B .B            | [2]<br>.B .B | [1]<br>.B .B<br>[2] | [0]<br>.B .B<br>[1] [0] |

| Possible data types                                     | 127 96 95 64 63 32 31 0<br>Vn     |    |      |     |    |              |              |              |              |                         |              |                         | 0            |                     |                         |

| 8-bit: FX<br>16-bit: FX/FP<br>32-bit: FX/FP             | 128-bit vector of 64-bit elements |    |      |     |    |              |              |              | .[           |                         |              | .D                      |              |                     |                         |

| 64-bit: FX/FP<br>128-bit: FX                            | 128-bit vector of 32-bit elements |    |      |     |    |              |              |              |              |                         | S<br>2]      | [0]<br>.S .S<br>[1] [0] |              |                     |                         |

|                                                         | 128-bit vector of 16-bit elements |    |      |     |    |              |              | .H<br>[7]    | .H<br>[6]    | н. н. н. н. н. н. н. н. |              |                         |              |                     |                         |

128-bit vector of 8-bit elements

.в.В

[15] ...

... [2] [1] [0]

.В

.B .B

Overview of the ISA extensions introduced to enhance compute capabilities

Remarks: See on the slide 2.1 Overview (5).

# 2.2.2 The GPR register set based SIMD extension

Neither this nor all subsequent 2.2.x Sections will be discussed.

#### 2.2.2 The GPR register set based SIMD extension (1)

## 2.2.2 The GPR register set based SIMD extension

### Evolution of the GPR register set in the ARM ISA -1

2.2.2 The GPR register set based SIMD extension (3)

# The GPR register sets in the ARMv3-ARMv7 and the ARM v8 ISA [63], [66]

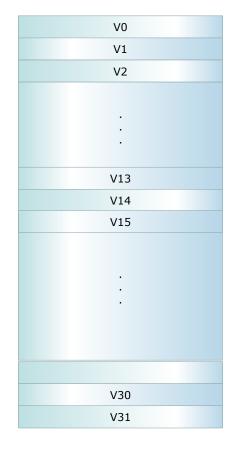

In the AArch64 mode the ARMv8 ISA version expands the number of GPRs from 13 32-bit registers to 31 64-bit wide registers, as shown in the next Figure.

GPRs in the ARMv3-ARMv7 and the ARMv8 AArch32 execution mode

GPRs in the ARMv8 AArch64 execution mode

### Introduction of the GPR register set based SIMD extension in the ARMv6 ISA

#### Introduction of the GPR register set based SIMD extension in the ARMv8 ISA

# The GPR register set based SIMD extension

- It supports FX-SIMD operations on 32-bit wide SIMD data in the GPR registers.

- Available instructions perform operations on 4xFX8 or 2xFX16 data in parallel.

- It is similar to Intel' s MMX x86 ISA extension from 1997.

- The GPR register set based SIMD extension as introduced into the ARMv6 ISA version provides only a modest performance boosting potential.

By contrast the subsequently, in the ARMv7 ISA version introduced, secondary register set based advanced SIMD (NEON) extension has a much higher performance boosting potential.

2. 2.2.3 Secondary register set based FP and SIMD extensions

2.2.3.1 Secondary reg. set based FP and SIMD extensions - Overview (1)

2.2.3 Secondary register set based FP and SIMD extensions

2.2.3.1 Secondary register set based FP and SIMD extensions - Overview

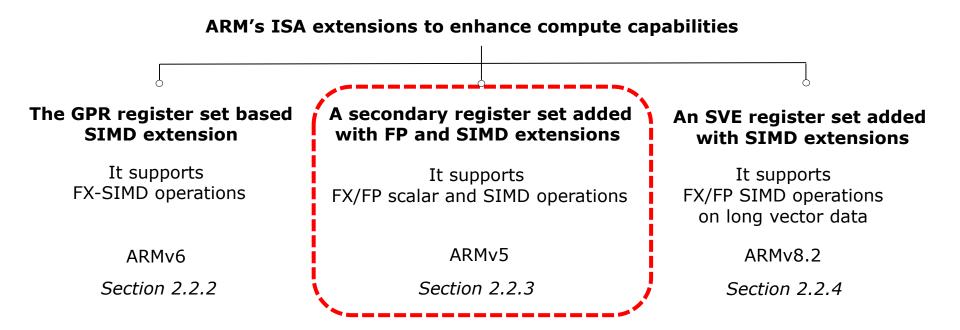

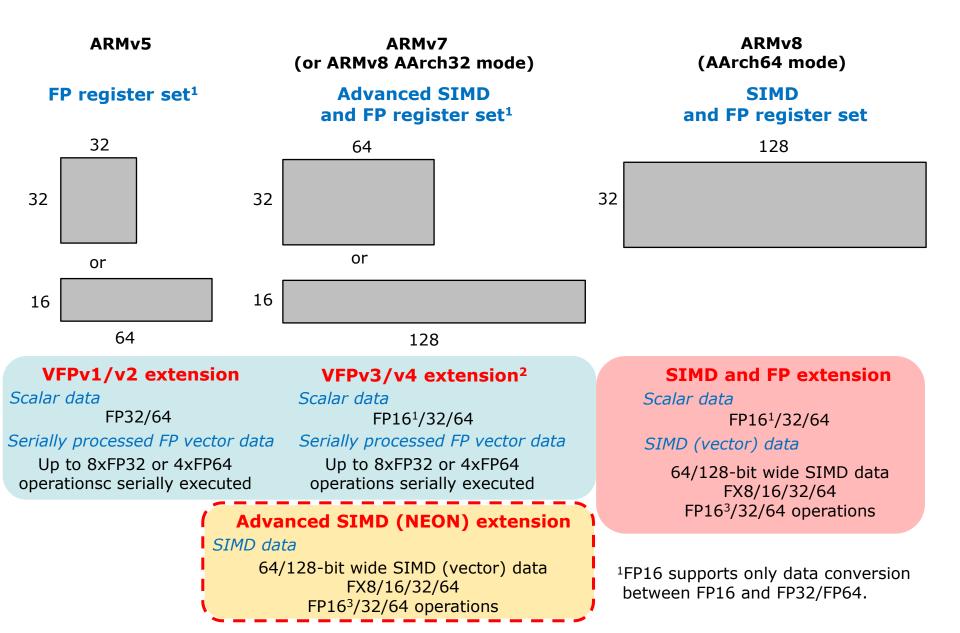

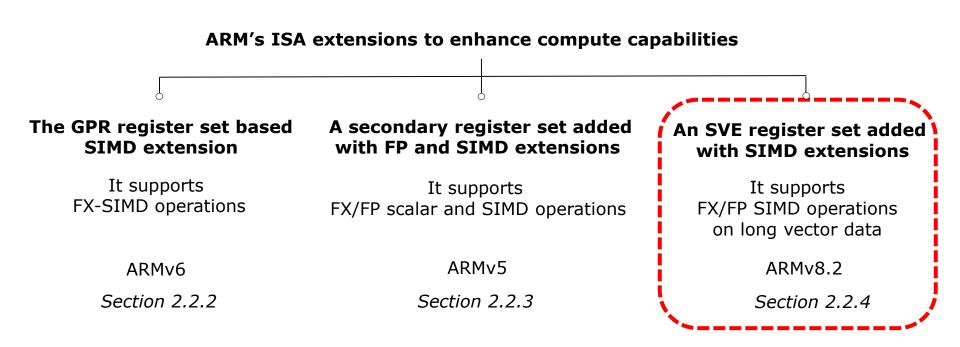

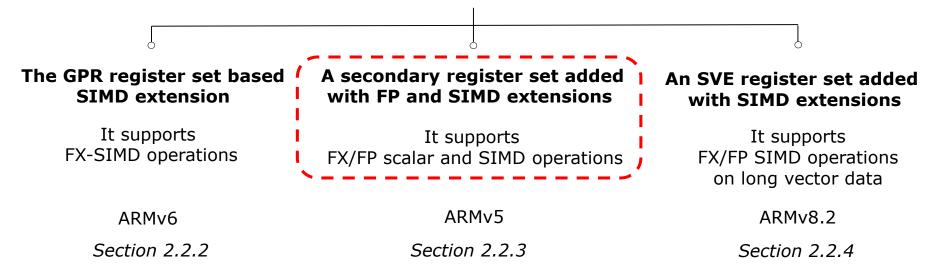

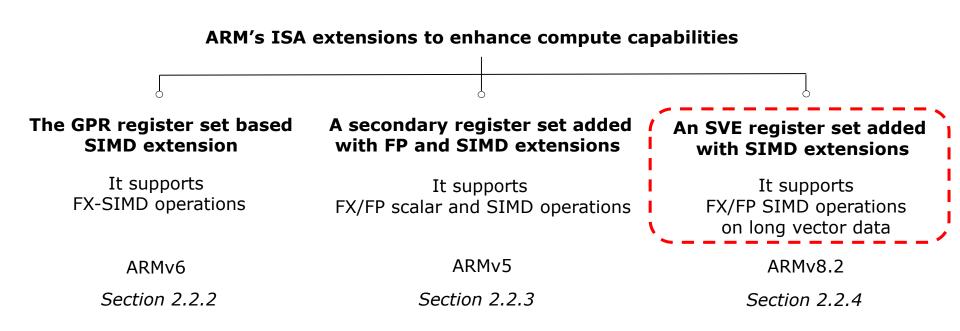

#### ARM's ISA extensions to enhance compute capabilities

2.2.3.1 Secondary reg. set based FP and SIMD extensions - Overview (2)

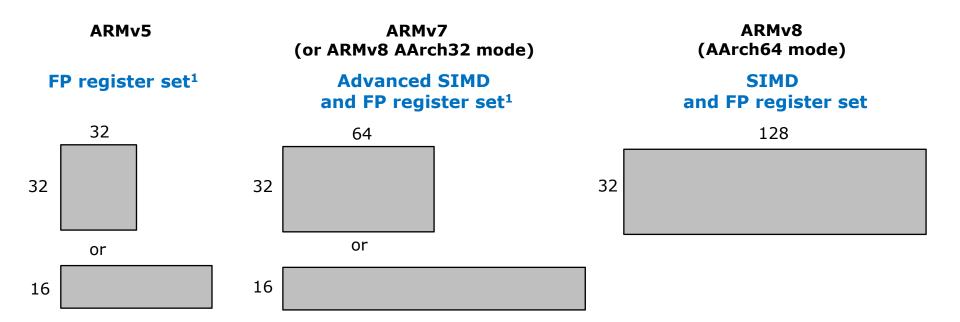

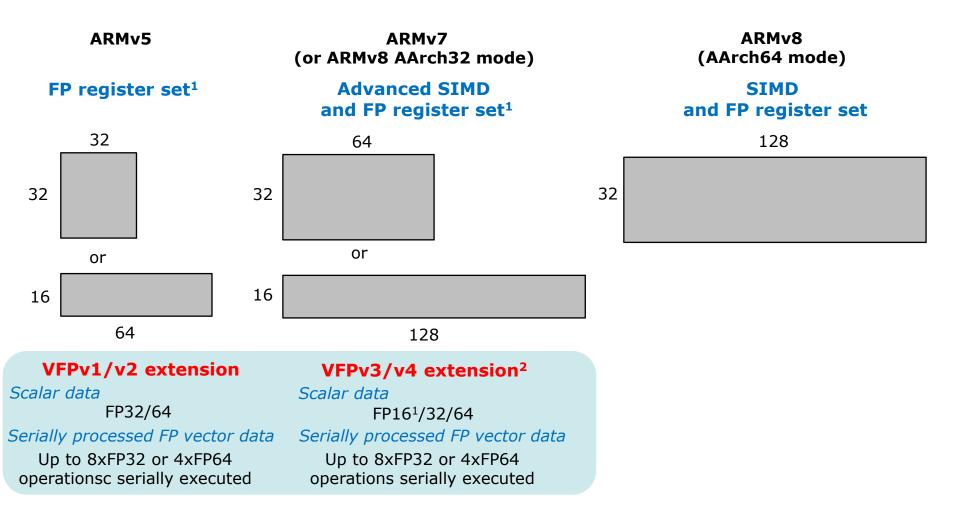

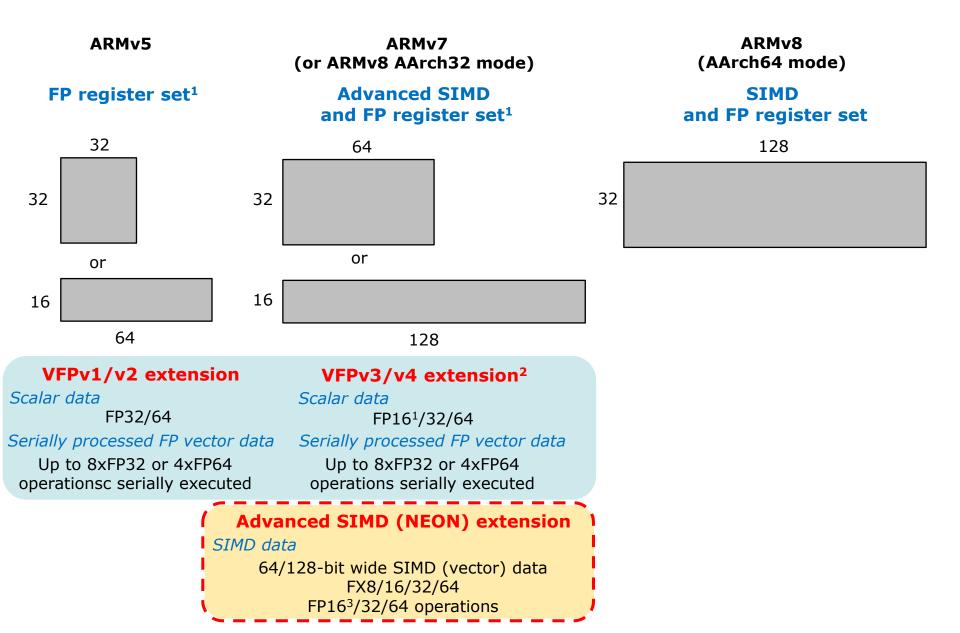

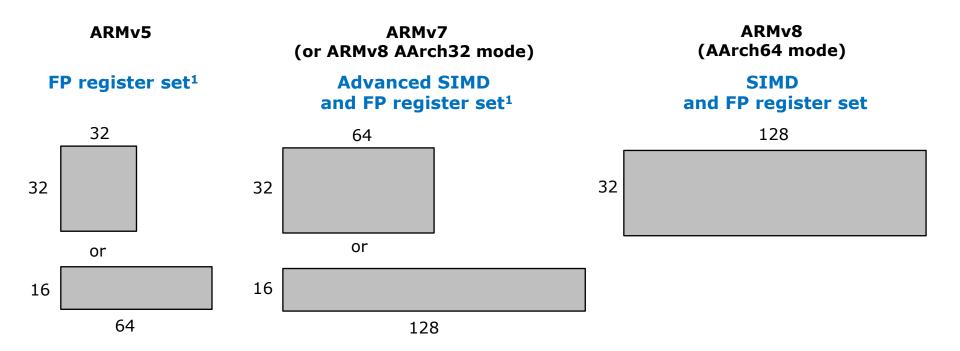

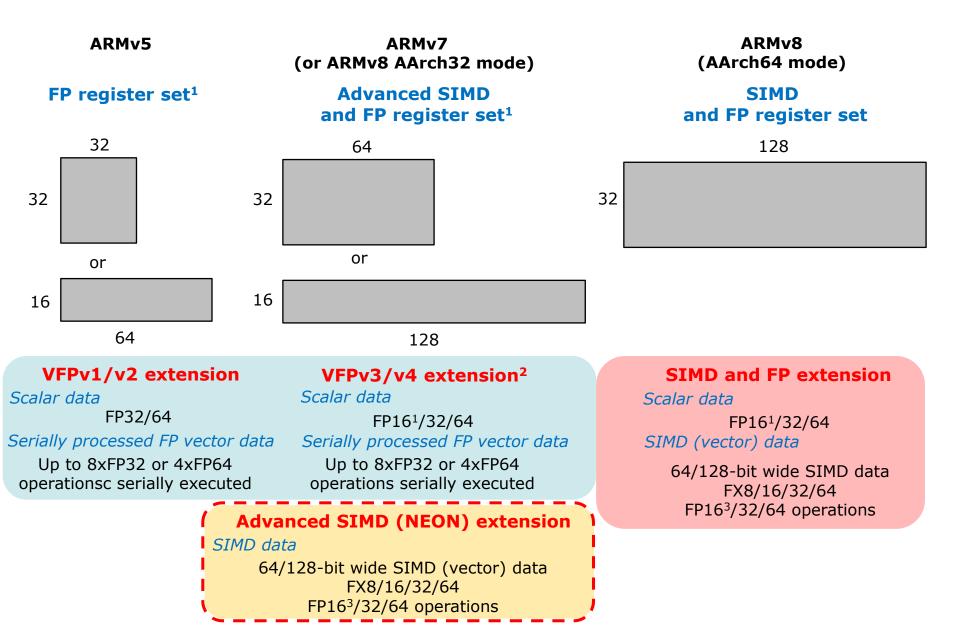

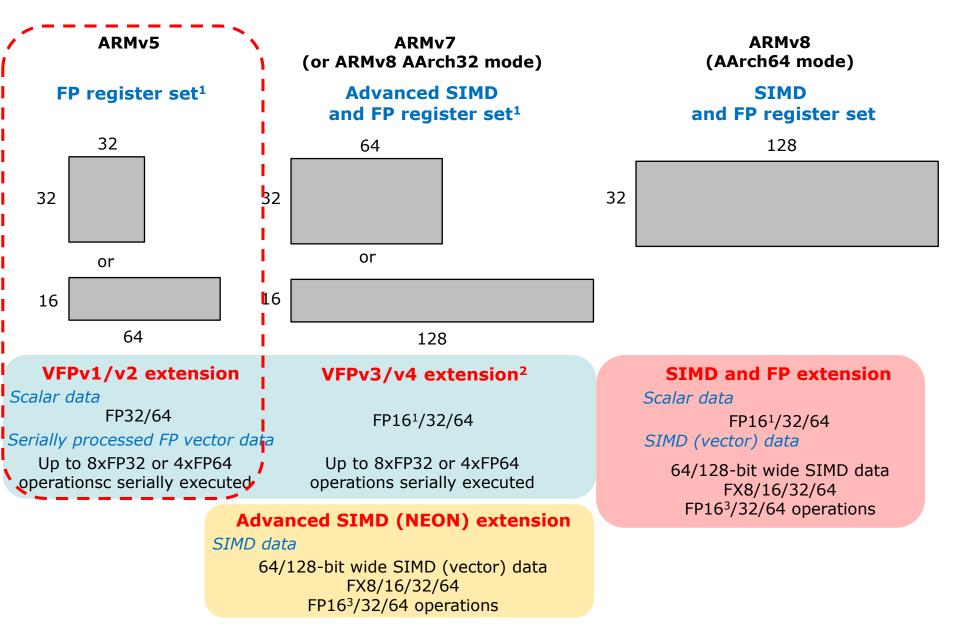

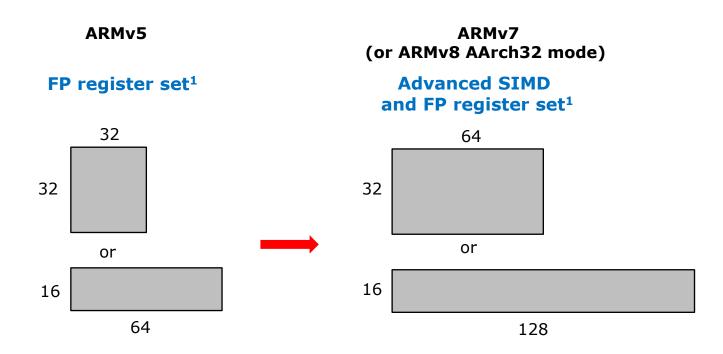

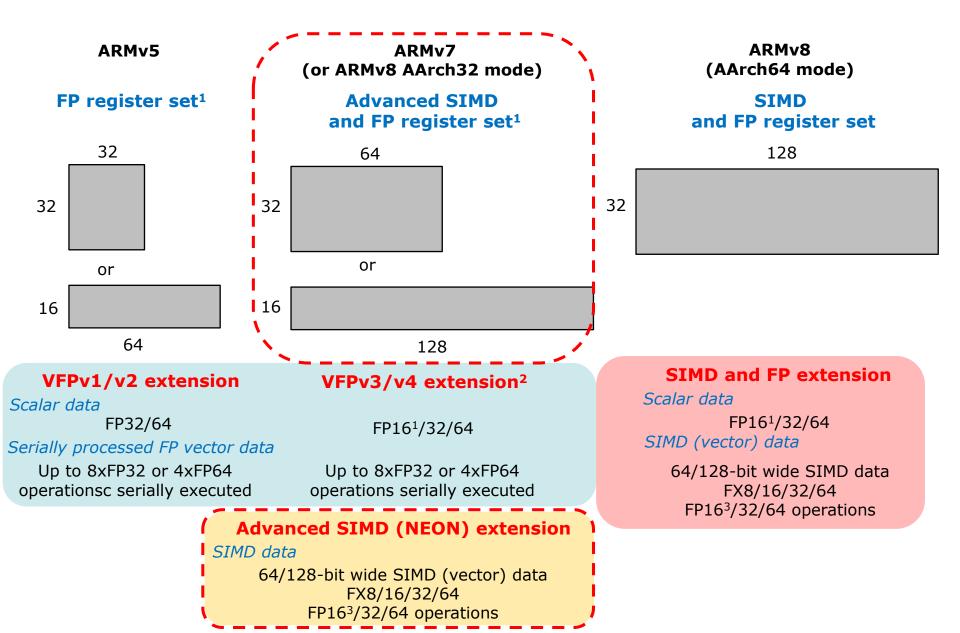

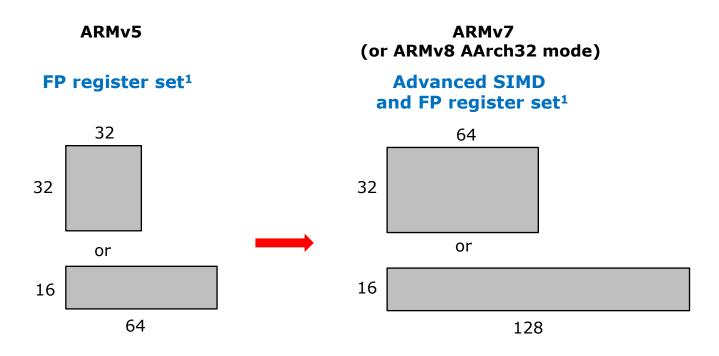

Designation and size of the secondary register set in the ARMv5 - ARMv8 ISAs

The secondary register set based FP and SIMD extensions - Overview

#### Remarks

<sup>1</sup>Certain models implement only half of the specified register numbers.

- <sup>2</sup>The implementation of the VFP3 or VFP4 extensions presumes the implemetation of the Advanced SIMD (NEON) extension.

- <sup>3</sup>In the VFP3/VFP4 extensions only conversions between FP16 and FP32 or FP64 are supported.

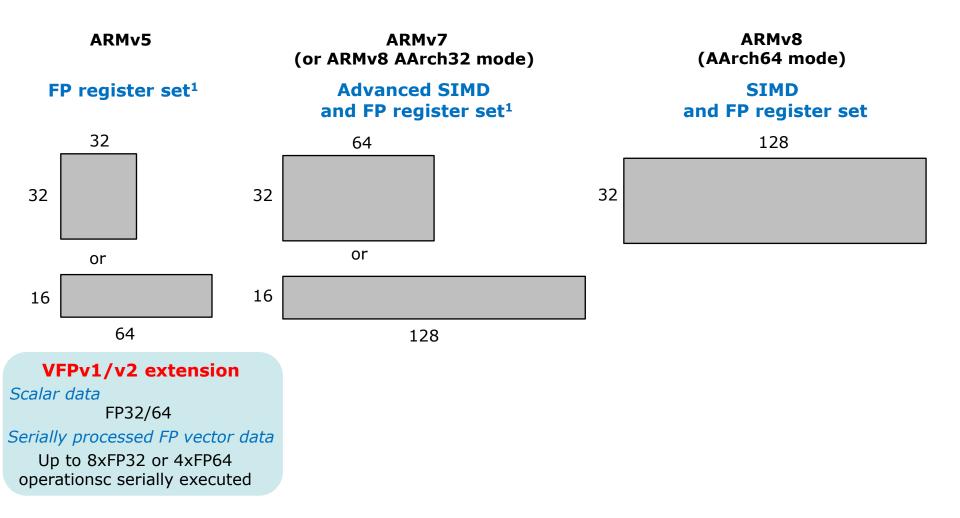

## 2.2.3.2 The VFPv1/v2 extensions

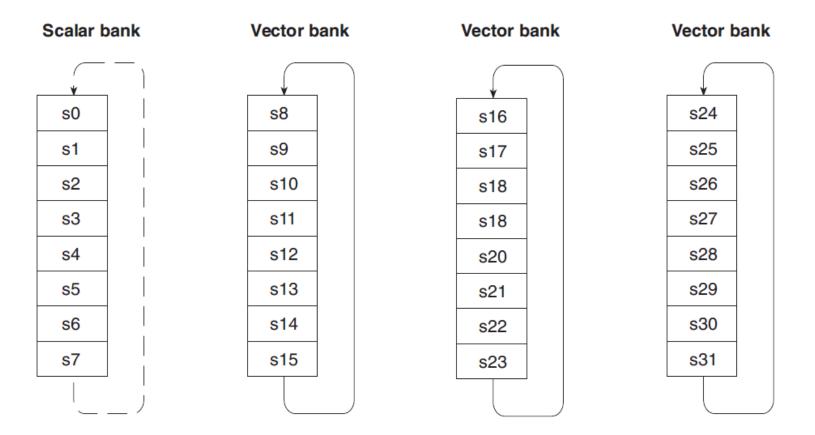

# The FP register set (as introduced in the ARMv5) [65]

• The new secondary register set is 32 x 32-bit or 16x64-bit wide and is organized as four register banks, each including 8 registers, as seen below.

Figure: Register banks of the VFP1 and VFP2 extensions [65]

# Use of the FP register set [65]

- The first bank is used to hold scalar operands whereas to remaining three banks vector operands.

- FP vector operands may refer to 2 to 8 registers from the same bank.

- The vector length is given in a specific field of a control register.

- The register numbers given in the instruction specify the first registers that contain the first operands and specify the first destination register.

Each successive element of the vector is taken by incrementing appropriately the register numbers.

- The peculiarity of the VFP extension is that the elements of the vector are processed sequentially rather than parallel as for usual SIMD execution.

# Example: Serially processed 5-element vector operation [65]

- In the example the input operands are taken from the registers s10...s14 and s18...s22, and the result is written into the registers s26...s30.

- The execution is sequential (like a hardware implemented subroutine).

### 2.2.3.3 The VFPv3/v4 extensions -1

# The VFPv3 and VFPv4 extensions -2

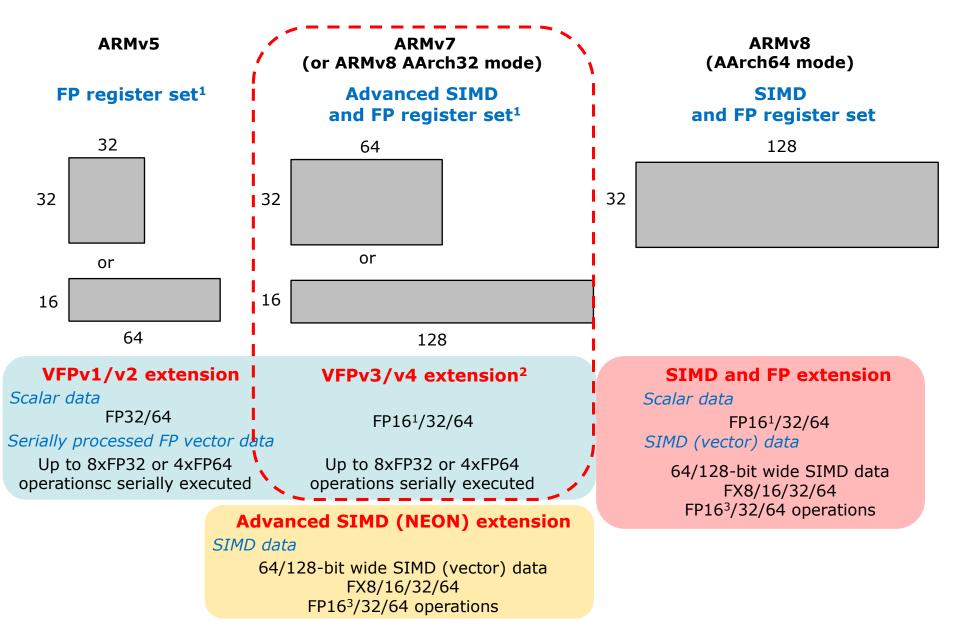

The underlying register set (called the Advanced SIMD and FP register set) is an extension of the previous FP register set and is shared by the NEON (Advanced SIMD and FP) extension.

Figure: Extension of the secondary register set in the ARMv7 ISA

It follows that the implementation of the VFPv3 or VFPv4 extensions presume the implementation of the Advanced SIMD (Neon) extension.

# The VFPv3 and VFPv4 extensions -3

- The VFPv3/v4 extensions support basically the same operations as the previous VFPv2 extension.

- The main enhancements of VFPv3/v4 are:

- VFPv3 support in addition FP16 (half-word FP) operations, nevertheless the supported operations are restricted only to conversions between FP16 and FP32 or FP64 data types.

- VFPv4's main enhancement is support of FMA (Fused Multiply Add) operations.

#### 2.2.3.3 The VFPv3/v4 extensions (4)

# Contrasting main features of the VFPv1/v2 and VFPv3/v4 extensions

VFP (Vector Floating Point) extensions

VFPv1/v2

Introduced in the ISA version ARMv5

- introduction of an FP register set (32x32 or 16x64 bit)

- supporting operations on

- scalar FP data (FP32/FP64) and

- serially processed FP vector data (up to 8xFP32 or 4xFP64)

Introduced in the ISA version ARMv6

VFPv3/v4

- doubling the size of the FP register set to 32x64 or 16x128 bit registers, and

- supporting oprations as in case of the previous vFPv2 version plus

- providing instructions that perform conversions between FP16 and FP32 or FP64 data (since the VFP3) and

- additionally FMA operations (in the VFP4 extension).

## 2.2.3.4 Advanced SIMD (NEON) extension -1

2.2.3.4 Advanced SIMD (NEON) extension (2)

2.2.3.4 The Advanced SIMD (NEON) extension of the ARMv7 -1

- NEON shares its register set with the VFPv3/v4 extension.

- The shared register set is called the Advanced SIMD and FP register set. It is an extension of the previous FP register set, as shown in the Figure below.

Figure: Extension of the secondary register set in the ARMv7 ISA

#### 2.2.3.4 Advanced SIMD (NEON) extension (3)

# 2.2.3.4 The Advanced SIMD (NEON) extension of the ARMv7 [11] -2

NEON is intended to accelerate multimedia and signal processing algorithms such as video encode/decode, 2D/3D graphics, gaming, speech or image processing.

# The Advanced SIMD (NEON) extension of the ARMv7 ISA [11] -2

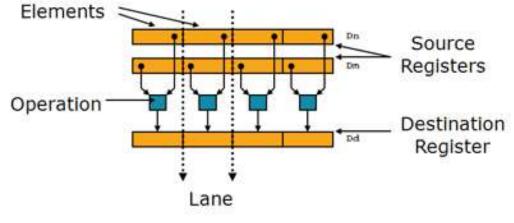

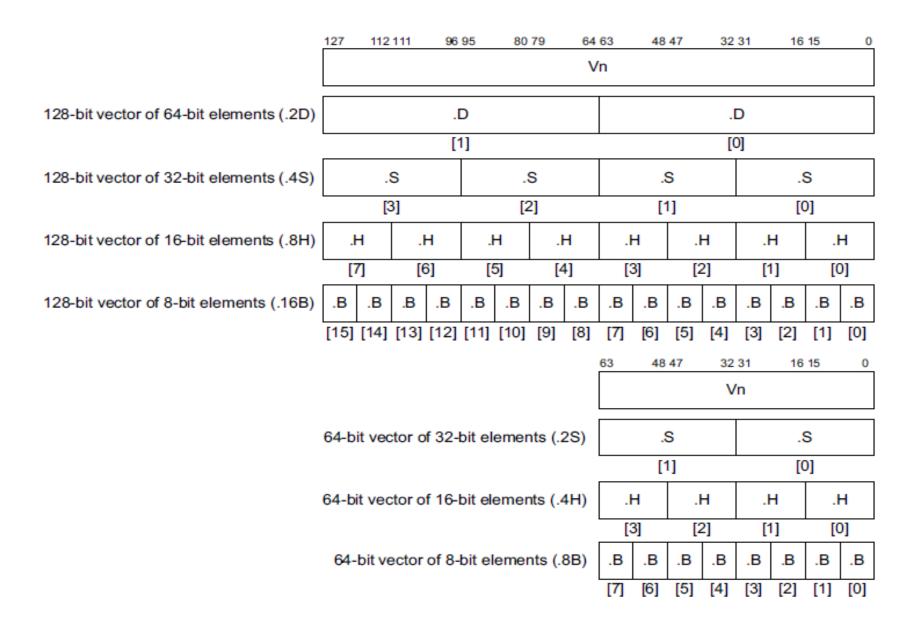

- NEON instructions operate on 64 or 128-bit wide vector data (SIMD data) held in the Advanced SIMD and FP register set.

- They perform the same operation on all data elements, as indicated below.

Figure: SIMD data [11]

- NEON instructions operate on 64 or 128-bit wide vectors with

- FX8/FX16/FX32/FX64 or

- FP16/FP32/FP64

data elements.

#### Remark

- For FP16 data NEON supports only conversions between FP16 and FP32/FP64 data.

- FP16 data operations are supported only in the Advanced SIMDv2 option.

#### 2.2.3.4 Advanced SIMD (NEON) extension (5)

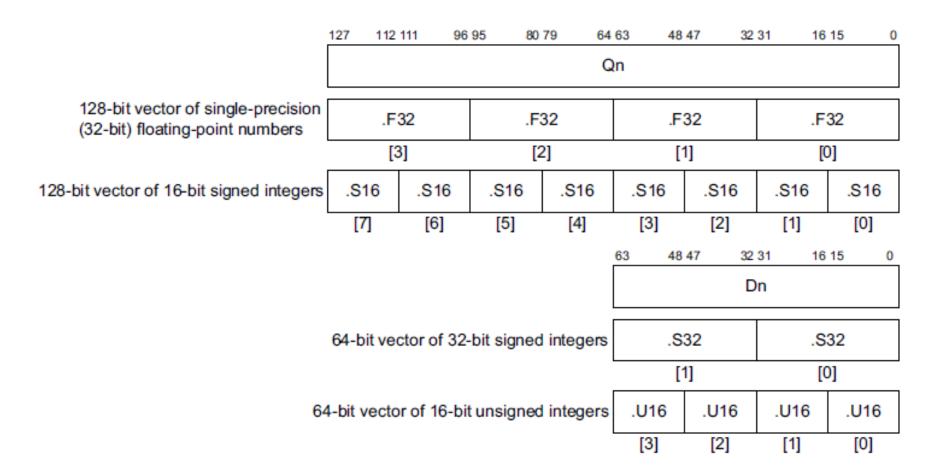

#### Example vector data formats of the Advanced SIMD (NEON) extension [86]

2.2.3.5 The SIMD and FP extension of the ARMv8 ISA in the AArch64 mode-1

2.2.3.5 The SIMD and FP extension of the ARMv8 ISA in AArch64 mode (2)

# The SIMD and FP extension of the ARMv8 ISA in the AArch64 mode -2

- The ARMv8 ISA version introduces major changes in the ARM architecture while maintaining a high level of consistency with previous versions of the architecture.

- ARMv8 has two distinct execution modes, as indicated below.

Aarch32 execution mode

Aarch64 execution mode

It supports two 32-bit instruction sets, the A32 and the T32 (Thumb) instructions sets.

In this mode the processor can run programs developed for previous ISA versions.

It supports a single 64-bit instruction set, called A64.

This is a fixed length powerful instruction set that uses 32-bit instruction encodings. 2.2.3.5 The SIMD and FP extension of the ARMv8 ISA in AArch64 mode (3)

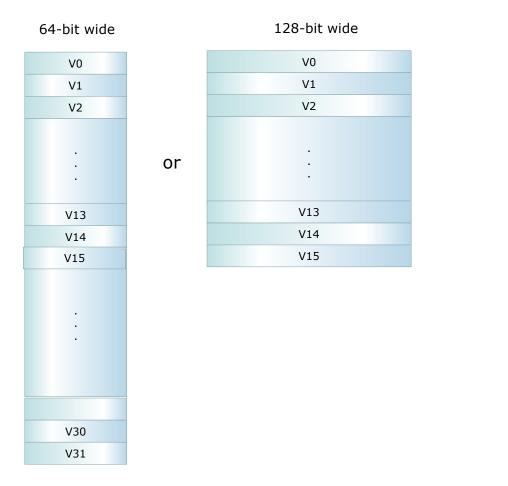

#### Extension of the secondary register set in the ARMv8 ISA [66]

# The AArch64 mode the ARMv8 ISA expands the number of the secondary registers from 32x64-bit or 16x64-bit (ARMv7 ISA) to 32x128-bit, as seen below.

128-bit wide

FP and advanced SIMD registers in the ARMv7 and ARMv8 AArch32 execution mode of the ARM ISA

SIMD and FP registers in the ARMv8 AArch64 execution mode of the ARM ISA

# Use cases of 64- and 128-bit wide SIMD data in the AArch64 mode [66]

2. 2.2.4 The SVE register set based SVE extension

#### 2.2.4 The SVE register set based SVE extension (1)

#### 2.2.4 The SVE register set based SVE extension

#### 2.2.4 The SVE register set based SVE extension (2)

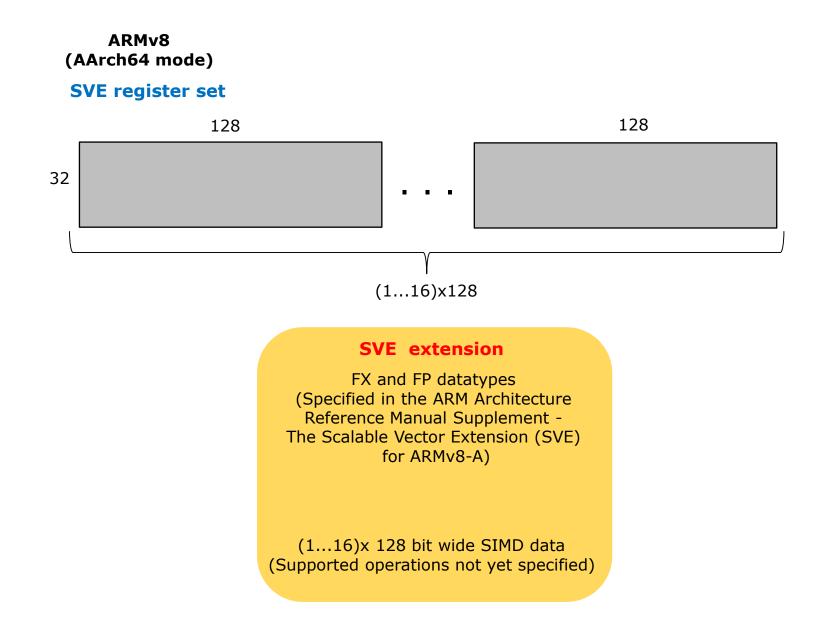

The SVE (Scalable Vector Extension) introduced into the AArch64 mode of the ARMv8 ISA [96]

- It was announced in 8/2016 (in the Hot Chips conference).

- General specification became available as the ARM Architecture Reference Manual Supplement - The Scalable Vector Extension (SVE) for ARMv8-A (β version in 3/2017).

- The vector length in SPE is a hardware choice from 1x128 bit to 16x128 bit, first implementions (e.g. by Fujitsu) choose 4x128 bit = 512 bit vector length.

- SVE is implemented only in the AArch64 version of ARMv8.

- SVE aims at HPC scientific workloads rather than media or image processing.

- It supports both FX and FP processing.

#### 2.2.4 The SVE register set based SVE extension (3)

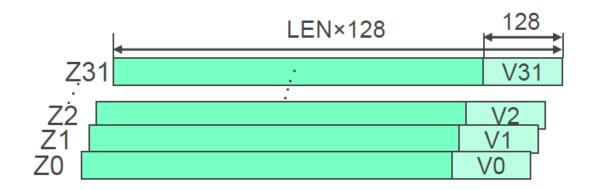

#### The SVE register set introduced in the AArch64 mode of the ARMv8 ISA

# Avalable SVE registers [96]

LEN: 1 to 16

#### 2.2.4 The SVE register set based SVE extension (5)

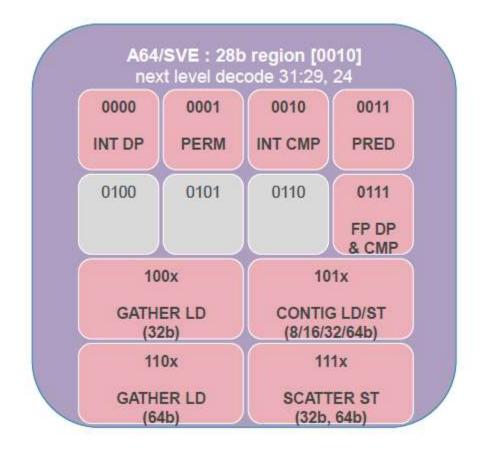

#### The SVE extension - Overview

# The SVE instruction set [96]

#### 2.2.4 The SVE register set based SVE extension (7)

# Example: Use of 256-bit vectors (either for FX or FP computations) [96]

# 256-bit vector, 64-bit elements 255 192 191 128 127 64 63 0 64b 64b 64b 64b 64b 64b 64b 64b

256-bit vector, packed 32-bit elements

| 255 | 192 | 191 | 128 |     | 64  | 63  | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 32b |

#### 2.2.4 The SVE register set based SVE extension (8)

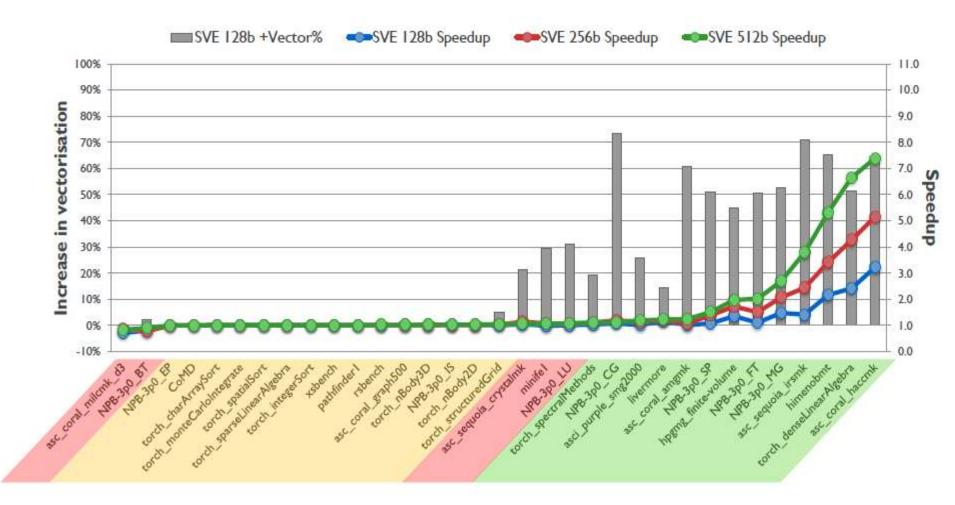

# Speed-up potential of SVE [96]

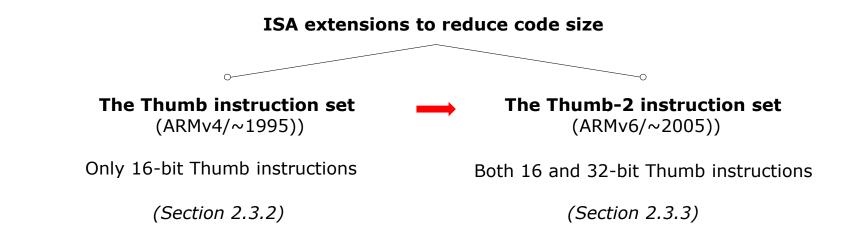

2.3 ISA extensions introduced to reduce code size

(Not discussed)

2.3.1 ISA extensions introduced to reduce code size - Overview (1)

2.3 ISA extensions introduced to reduce code size2.3.1 ISA extensions introduced to reduce code size - Overview (1)

2.3.1 ISA extensions introduced to reduce code size - Overview (2)

ISA extensions introduced to reduce code size - Overview (2) (Based on [64]

Remarks: See on the slide 2.1 Overview (5)

2.3.1 ISA extensions introduced to reduce code size - Overview (3)

#### ISA extensions introduced to reduce code size - Overview (3)

# 2.3.2 The Thumb instruction set [67]

- This is an alternative 16-bit instruction set that provides typically 35 to 40 % better code density than traditional ARM code but reduces performance slightly, e.g. by 10 %.

- It has been introduced in the ARMv4 ISA.

- Processors with the T suffix provide beyond the default 32-bit ARM also the 16-bit Thumb instruction set.

- Thumb instructions are 16-bit long, most 32-bit ARM instructions can be recoded

- to a single 16-bit Thumb instruction format.

- The Thumb instruction set is a subset of the ARM instruction set.

- There is a special instruction for entering the Thumb state (BX).

- Compilers are usually able to generate code optinally either for the ARM or the Thumb ISA.

- In the Thumb instructon set there are only 8 GPRs available for the programmer, as shown in the next Figure.

#### 2.3.2 The Thumb instruction set (2)

Available GPR register sets in the ARM and the Thumb ISA [63]

# 2.3.3 The Thumb-2 instruction set [79]

- It was introduced along with the ARM1156T2-S processor in 2005.

- Thumb-2 is a superset of the 16-bit ARMv6 Thumb iSA.

- It adds several new 16-bit instructions and also 32-bit instructions that can be freely intermixed in a program.

- The enhancements allow Thumb-2 to more efficiently cover the functionality of the ARM instruction set.

- In subsequent processors Thumb-2 replaced the Thumb instruction set.

2.4 ISA extensions to speed up the execution of bytecodes

(Not discussed)

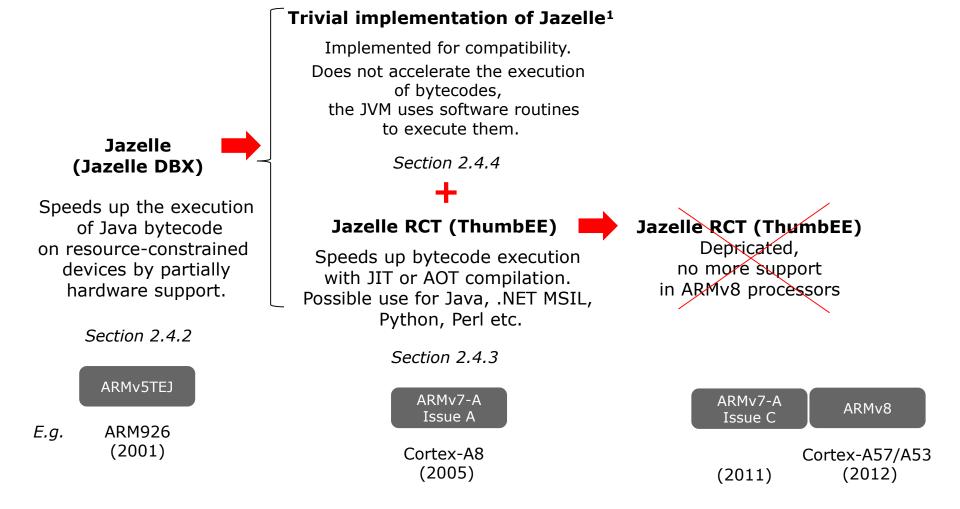

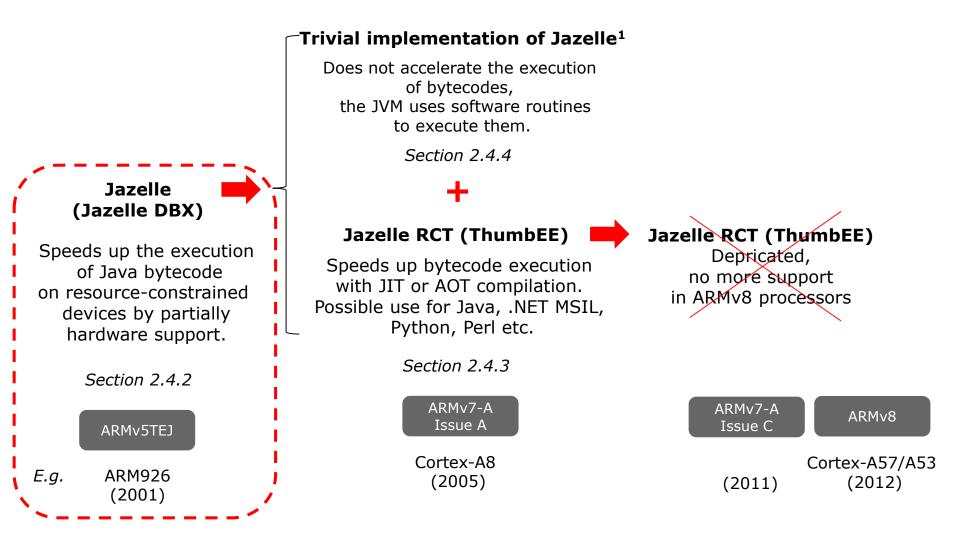

2.4.1 ISA extensions to speed up the execution of bytecodes - Overview (1)

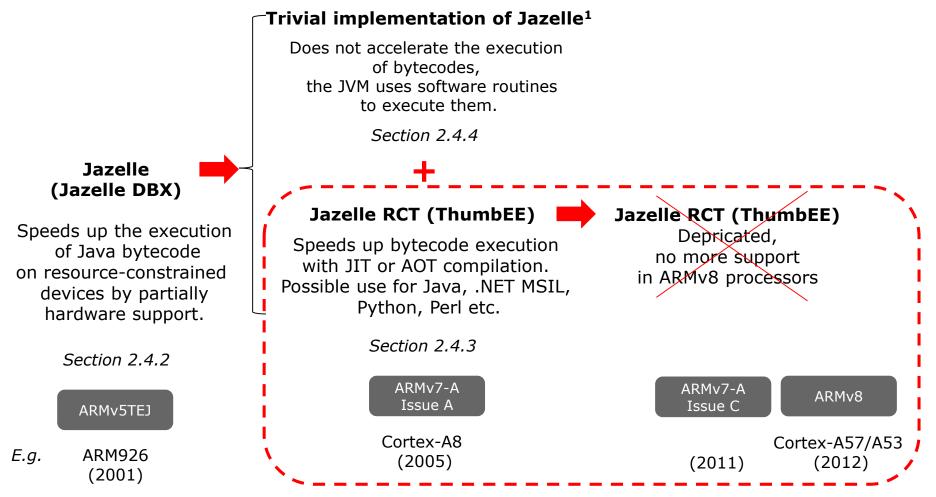

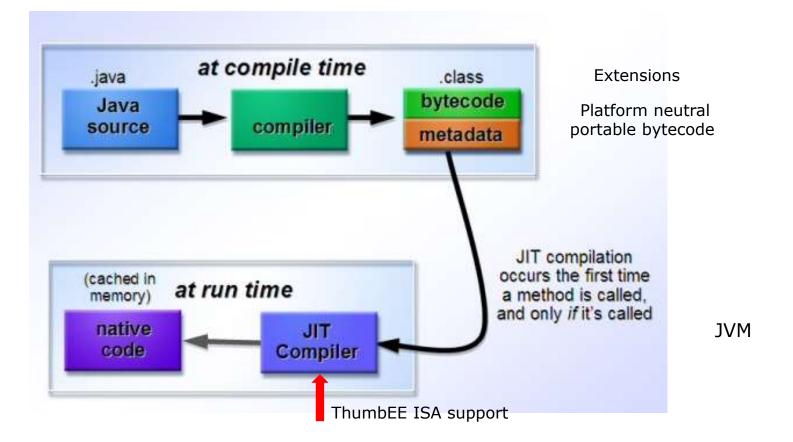

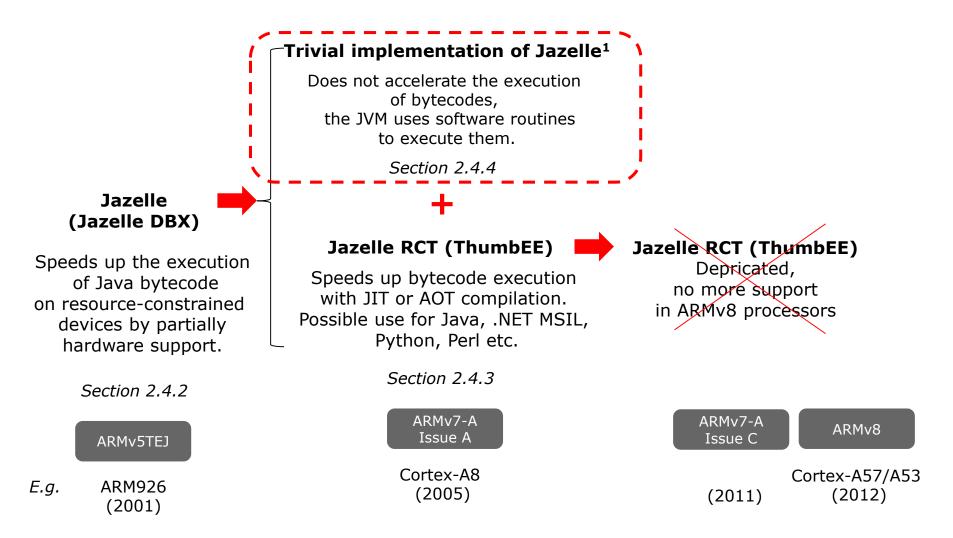

2.4 ISA extensions introduced to speed up the execution of bytecodes2.4.1 ISA extensions introduced to speed up the execution of bytecodes

Overview (1)

2.4.1 ISA extensions to speed up the execution of bytecodes - Overview (2)

ISA extensions introduced to speed up the execution of bytecodes Overview (2) (Based on [64])

Remarks: See on the slide 2.1 Overview (5).

2.4.1 ISA extensions to speed up the execution of bytecodes - Overview (3)

#### ISA extensions to speed up the execution of bytecodes - Overview (3)

<sup>1</sup>A few ARMv7 processors, such as the Cortex-A5 and the Cortex-A9 support Jazelle DBX as an option.

#### 2.4.2 Jazelle (Jazelle DBX) (1)

# 2.4.2 Jazelle (Jazelle DBX) -1

<sup>1</sup>A few ARMv7 processors, such as the Cortex-A5 and the Cortex-A9 support Jazelle DBX as an option.

#### 2.4.2 Jazelle (Jazelle DBX) (2)

# 2.4.2 Jazelle (Jazelle DBX) -2

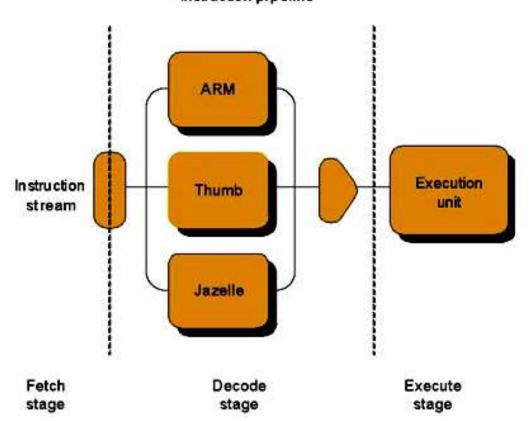

It is ARM's third ISA option, introduced in the ARMv5TEJ ISA (in 2001), as indicated below.

Instruction pipeline

Figure: The Jazelle ISA extension as ARM's third ISA alternative [67]

It aims at accelerating the execution of Java bytecode.

# 2.4.2 Jazelle (Jazelle DBX) (3)

# Java bytecode

- It is one kind of bytecodes.

- Bytecodes are compact 1-byte codes written for a stack based virtual machine (virtual ISA).

All opcodes are one byte long followed by optional parameters.

# 2.4.2 Jazelle (Jazelle DBX) (4)

Part of a Java bytecode [80]

| ;                        | section.constpool:  |                       |  |  |

|--------------------------|---------------------|-----------------------|--|--|

| 0x00000000               |                     | breakpoint            |  |  |

| 0x00000001               | fe                  | impdep1               |  |  |

| 0x00000002               | babe000300          | invokedynamic (48639) |  |  |

| 0×00000007               | 2d                  | aload_3               |  |  |

| 0x00000008               | 00                  | 100                   |  |  |

| 0x00000009               |                     | lload 3               |  |  |

| 0x0000000a               |                     | lconst_1              |  |  |

| 0x0000000b               | 00                  | (DOD)                 |  |  |

| 0x0000000c               | 07                  | iconst_4              |  |  |

| 0x0000000d               | 00                  | hop                   |  |  |

| 0x0000000e               | 1009                | bipush 9              |  |  |

| 0x00000010               | 00                  |                       |  |  |

| 0x00000011               | 110012              | sipush 0x11 0x0       |  |  |

| 0x00000014               | 08                  | iconst_5              |  |  |

| 0x00000015               |                     | (NOB)                 |  |  |

| 0x00000016               | 130a00              | ldc_w "Code"          |  |  |

| 0x00000019               | 110014              | sipush 0x11 0x0       |  |  |

| 0x0000001c               | 0a                  | lconst_1              |  |  |

| 0x0000001d               |                     |                       |  |  |

| 0x0000001e               | 1500                | iload 0               |  |  |

| 0x00000020               | 1607                | lload 7               |  |  |

| 0x00000022<br>0x00000023 | 00                  |                       |  |  |

| 0x00000023               | 1707                | fload 7               |  |  |

| 0x00000025               | 00                  |                       |  |  |

| 0x00000026               | 1801                | dload 1               |  |  |

| 0x00000028               | 00                  |                       |  |  |

| 0x00000029               | 06                  | iconst_3              |  |  |

| ;                        |                     |                       |  |  |

| 0x0000002a               | .string "init" ;    |                       |  |  |

| 0x0000030                |                     | aconst_null           |  |  |

| 0×00000031               |                     |                       |  |  |

| 0x00000032               |                     | iconst_0              |  |  |

| ;                        |                     |                       |  |  |

| 0x00000033               | .string "V" ; len=3 |                       |  |  |

|                          |                     |                       |  |  |

The computational model assumed for bytecodes

The computational model of bytecodes presumes a stack based execution, i.e. operands are first loaded into the stack and operations will be executed on the operands being in the stack.

#### 2.4.2 Jazelle (Jazelle DBX) (6)

# Principle of generating and executing Java bytecode -1 [81]

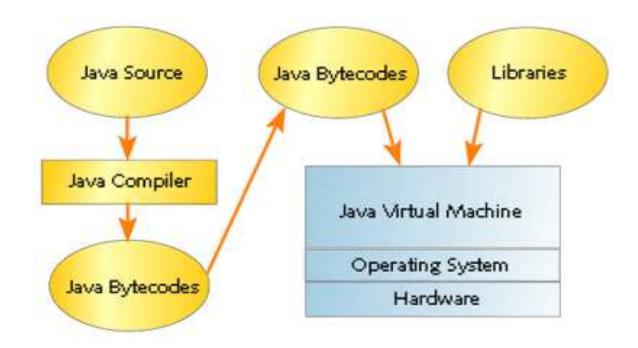

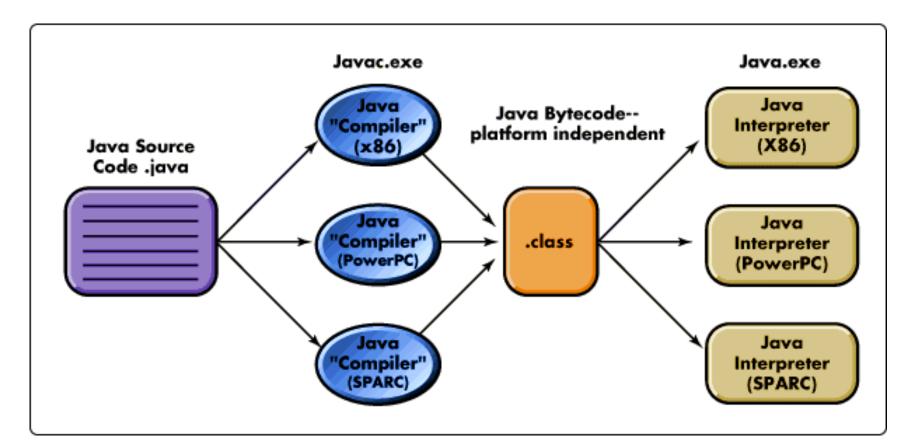

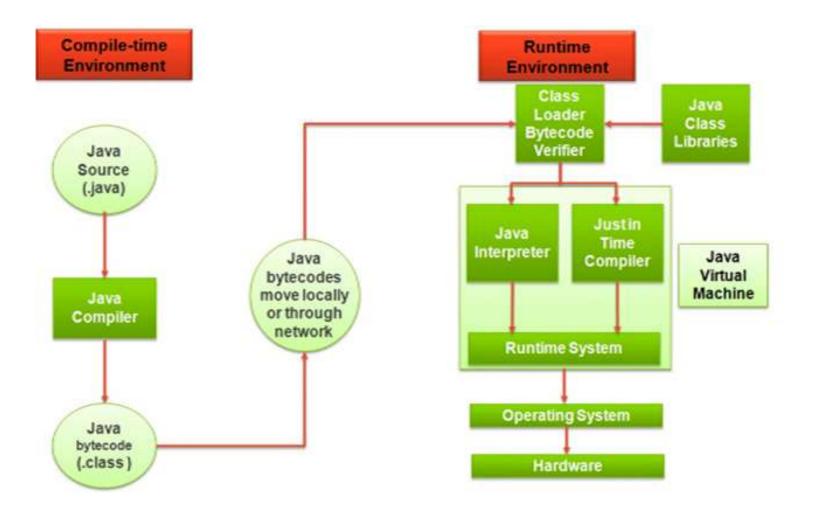

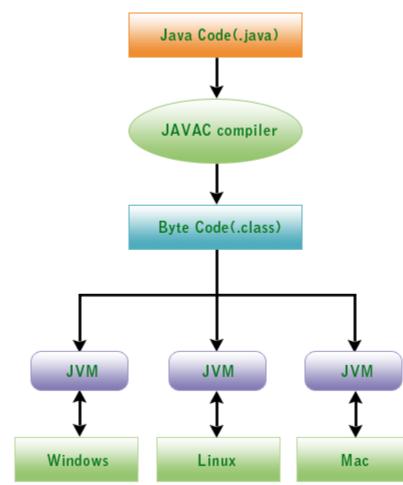

- Bytecodes are generated by compiling a source code assuming a virtual ISA that is underlying the considered bytecode and is not bound to any real ISA, like the ARM or x86 ISA.

- So bytecodes can not be directly run on any processor, i.e. they are a kind of pseudocode that can be executed by a virtual machine, as indicated in the next Figure for the Java bytecode.

#### 2.4.2 Jazelle (Jazelle DBX) (7)

# Principle of generating and executing Java bytecode -2 [81]

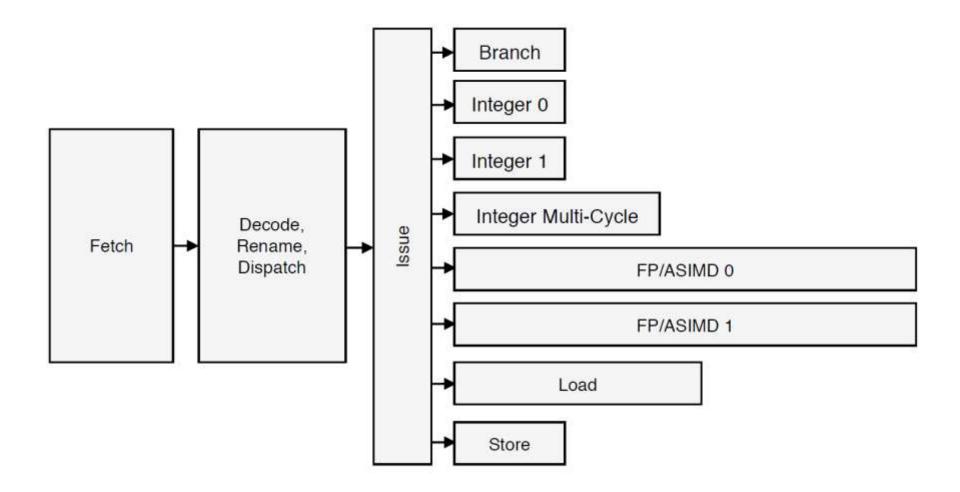

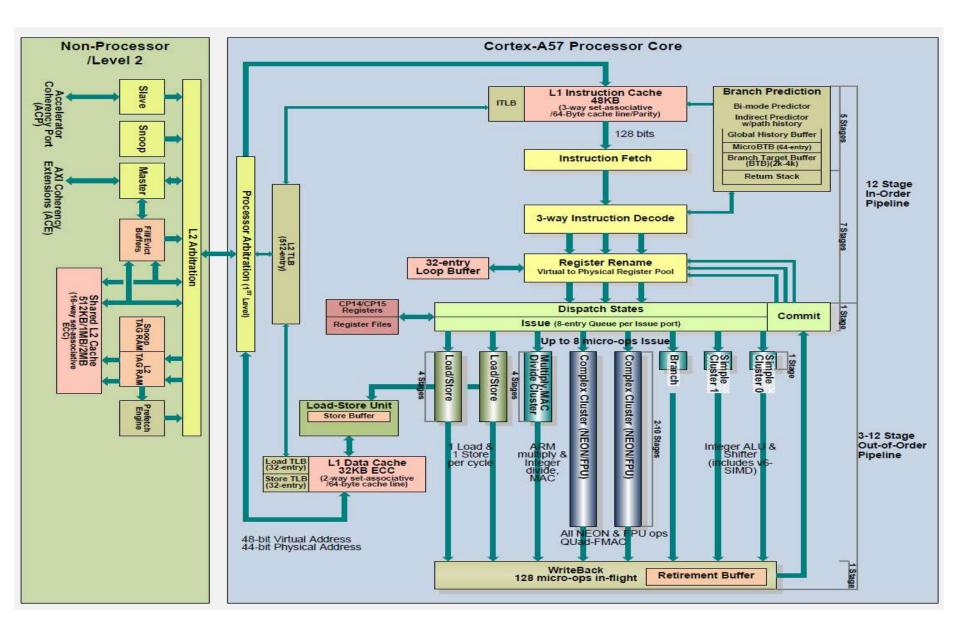

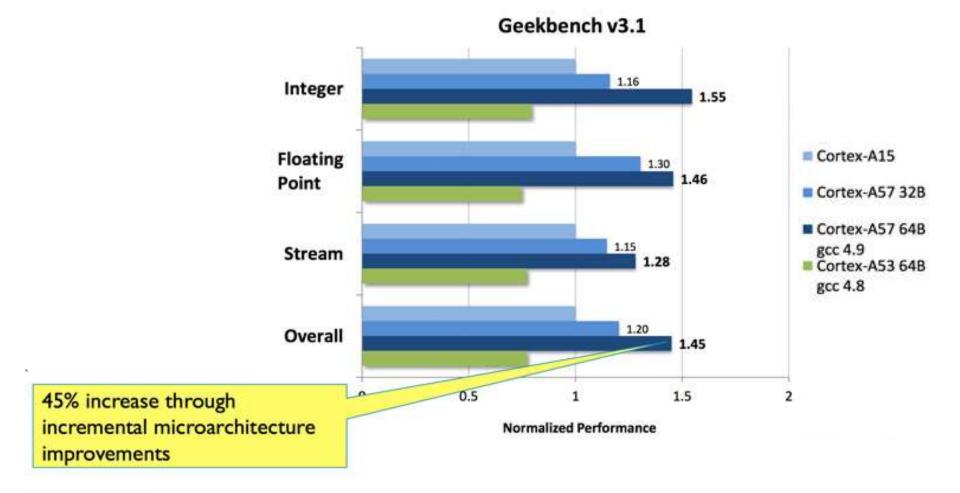

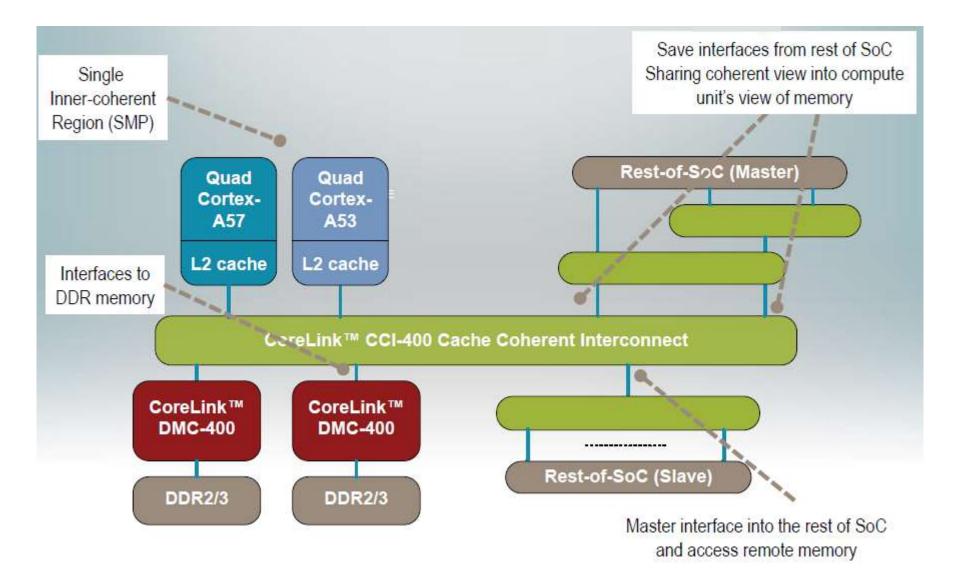

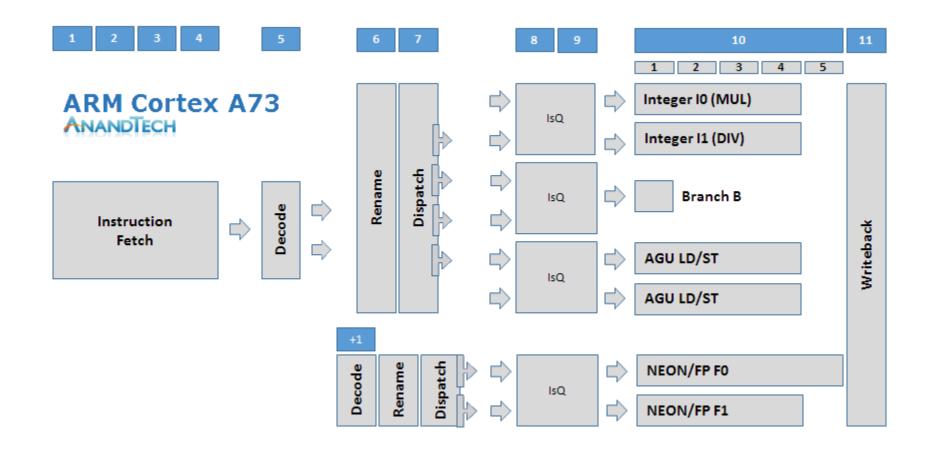

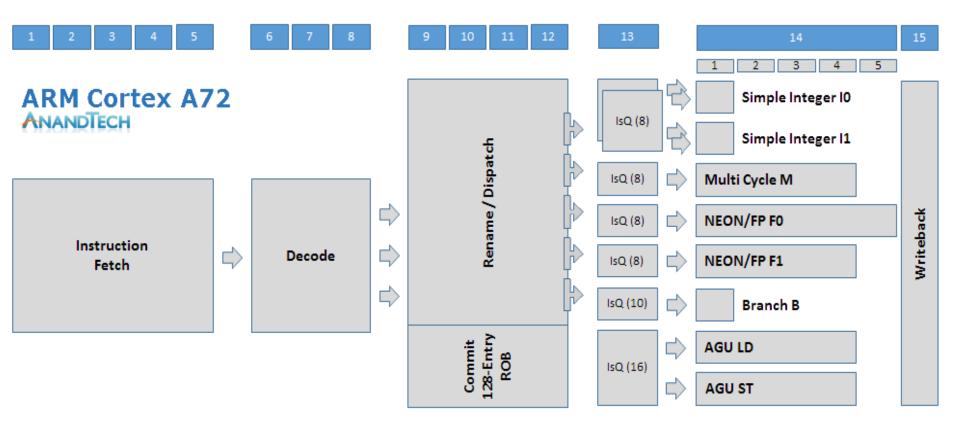

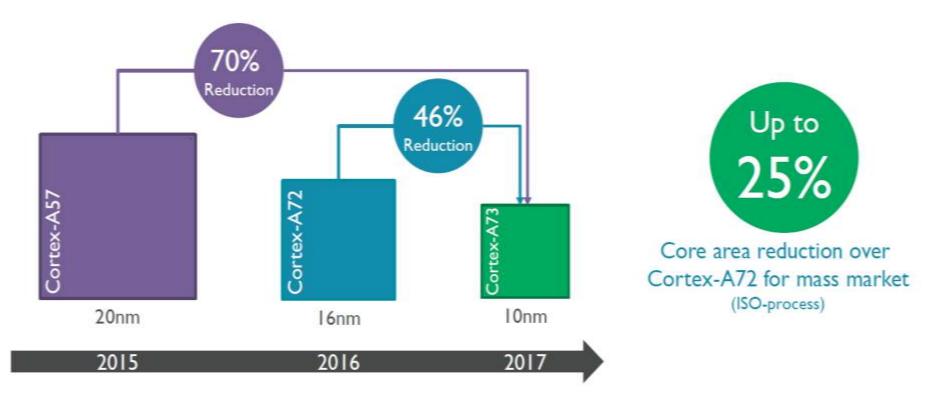

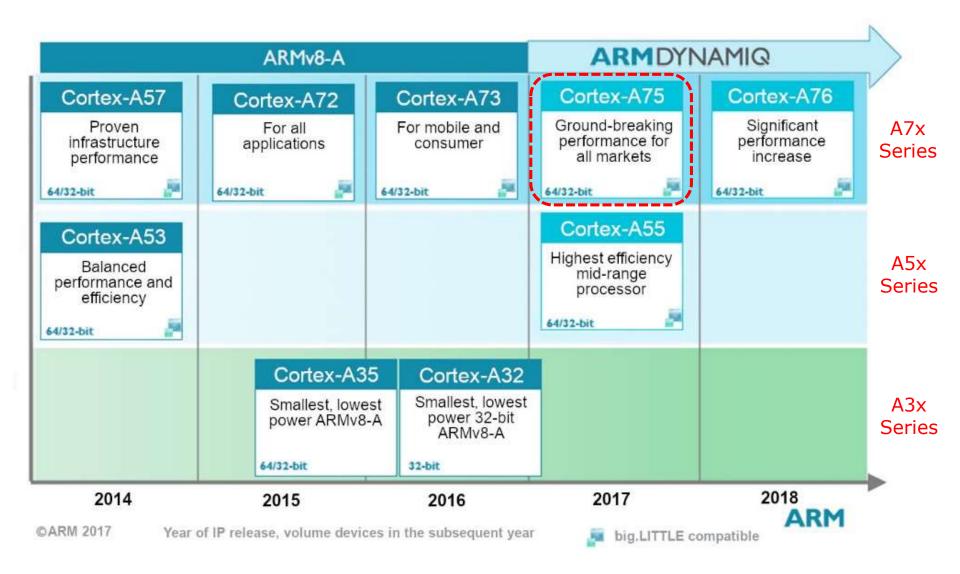

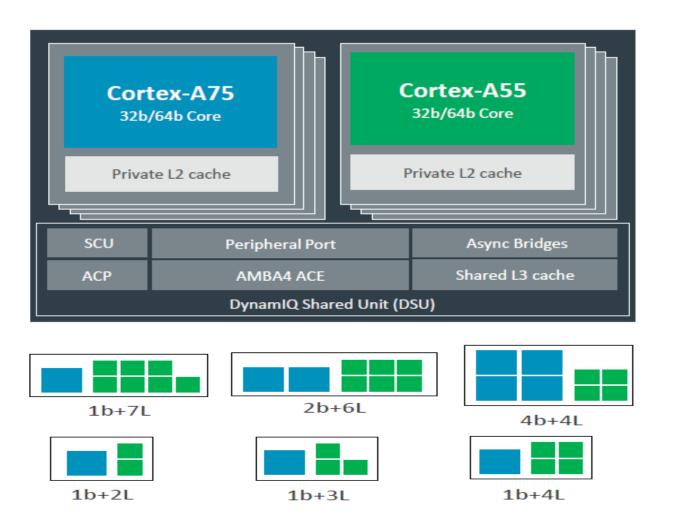

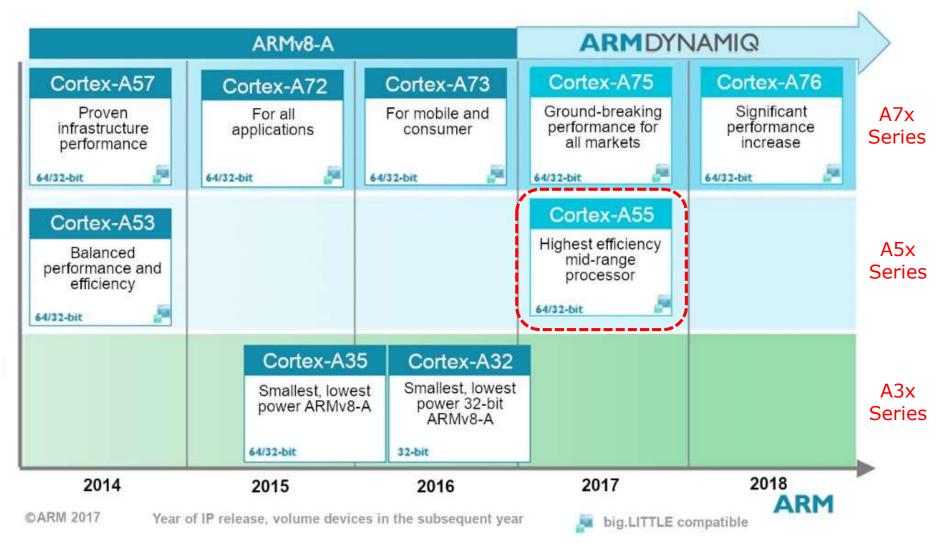

#### 2.4.2 Jazelle (Jazelle DBX) (8)