Samsung's mobile lines Dezső Sima

Vers. 1.2

Mai 2018

#### Contents

- 1. Samsung's earliest mobile SOCs

- 2. Overview of Samsung's quad- and octa core mobile SOCs

- 3. Quad- and octa core SMPs

- 4. Octa core big.LITTLE mobile SOCs with exclusive cluster allocation

- 5. Octa core big.LITTLE mobile SOCs supporting GTS

- 6. References

1. Samsung's earliest mobile SOCs

# 1. Samsung's earliest mobile SOCs -1 [71]

| Model<br>Number | Technology      | CPU ISA | CPU                                              | GPU               | Memory<br>tech.           | Availa<br>bility | Utilizing devices                                                                                                        |

|-----------------|-----------------|---------|--------------------------------------------------|-------------------|---------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------|

| S3C44B0         | 0.25 μm<br>CMOS | ARMv4   | 66 MHz<br>single-core ARM7<br>(ARM7TDI)          | LCD<br>controller | FP, EDO,<br>SDRAM         | 2000             | Juice Box, Danger Hiptop                                                                                                 |

| S5L2010         |                 | ARMv5   | 176 MHz<br>single-core ARM9<br>(ARM946E-S)       | LCD<br>controller | SDRAM,<br>EDO             |                  |                                                                                                                          |

| S3C2410         | 0.18 µm<br>CMOS | ARMv4   | 200/266 MHz<br>single-core ARM9<br>(ARM920T)     | LCD<br>controller | SDRAM                     | 2003             | HP iPAQ H1930/H1937/H1940/rz1717,,<br>Acer n30/n35/d155, Palm Z22,<br>LG LN600, Typhoon MyGuide 3610 GO                  |

| S3C2412         | 0.13 μm<br>CMOS | ARMv5   | 200/266 MHz<br>single-core ARM9<br>(ARM926EJ-S)  | LCD<br>controller | mSDRAM                    |                  |                                                                                                                          |

| S3C2413         | 0.13 μm<br>LP   | ARMv5   | 266 MHz<br>single-core ARM9<br>(ARM926EJ-S)      | LCD<br>controller | mSDRAM,<br>mDDR           |                  |                                                                                                                          |

| S3C2440         | 0.13 μm<br>CMOS | ARMv4   | 300/400/533 MHz<br>single-core ARM9<br>(ARM920T) | LCD<br>controller | SDRAM                     | 2004             | HP iPAQ rx3115/3415/3417/3715,<br>Everex E900, Acer n300/311,<br>Typhoon MyPhone M500,<br>Mio p550/P350/C710 Digi-Walker |

| S3C22442        | 0.13 μm<br>CMOS | ARMv4   | 300/400 MHz<br>single-core ARM9<br>(ARM920T)     | LCD<br>controller | mSDRAM                    |                  |                                                                                                                          |

| S3C24431        |                 | ARMv4   | 400/533 MHz<br>single-core ARM9<br>(ARM920T)     | LCD<br>controller | SDRAM,<br>mSDRAM,<br>mDDR | 2007             | Asus R300/R600/R700,<br>Mio Digi-Walker (C620T),<br>LG LN8xx,<br>JL7220, Navigon 8300/8310                               |

# Samsung's earliest mobile SOCs -2 [71]

| Model<br>Number | Technology       | CPU<br>ISA | CPU                                                    | GPU                                  | Memory<br>tech.                    | Availa<br>bility | Utilizing devices                                                                                                         |

|-----------------|------------------|------------|--------------------------------------------------------|--------------------------------------|------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------|

| S5L8900         | 90 nm            | ARMv6      | 412 MHz<br>single-core ARM11                           | PowerVR<br>MBX Lite                  | eDRAM                              | 2007             | Apple iPhone,<br>Apple iPod touch 1G,<br>Apple iPhone 3G                                                                  |

| S3C2416         | 65 nm LP         | ARMv5      | 400 MHz<br>single-core ARM9<br>(ARM926EJ)              | 2D graphics<br>accelerator           | SDRAM,<br>mSDRAM,<br>mDDR,<br>DDR2 | 2008             | iconX G310, HP Prime                                                                                                      |

| S3C2450         | 65 nm LP<br>CMOS | ARMv5      | 400/533 MHz<br>single-core ARM9<br>(ARM926EJ)          | 2D graphics<br>accelerator           | SDRAM,<br>mSDRAM,<br>mDDR,<br>DDR2 | 2008             | Mio<br>Moov 500/510/560/S568/580,<br>Getac PS535F, MENQ EasyPC<br>E720/E790,<br>Hivision PWS0890AW,SMiT<br>MTV-PND530 8GB |

| S3C6410         | 65 nm LP         | ARMv6      | 533/667/800 MHz<br>single-core ARM11<br>(ARM1176ZJF-S) | FIMG 3DSE<br>graphics<br>accelerator | mSDRAM,<br>mDDR                    | 2009             | Samsung S5620 Monte                                                                                                       |

| S5P6442         | 45 nm            | ARMv6      | 533/667 MHz<br>single-core ARM11                       | FIMG 3DSE<br>graphics<br>accelerator |                                    | 2010             |                                                                                                                           |

| S5P6450         |                  | ARMv6      | 533/667/800 MHz<br>single-core ARM11<br>(ARM1176JZF-S) | 3D graphics accelerator              | mDDR,<br>mDDR2,<br>LPDDR           | 2010             |                                                                                                                           |

| S5PC100         | 65 nm            | ARMv7      | 667/833 MHz<br>single-core ARM<br><u>Cortex-A8</u>     | PowerVRSG<br>X535                    | LPDDR2,<br>DDR2                    | 2009             | Apple iPhone 3GS                                                                                                          |

2. Overview of Samsung's quad- and octa core mobile SOCs

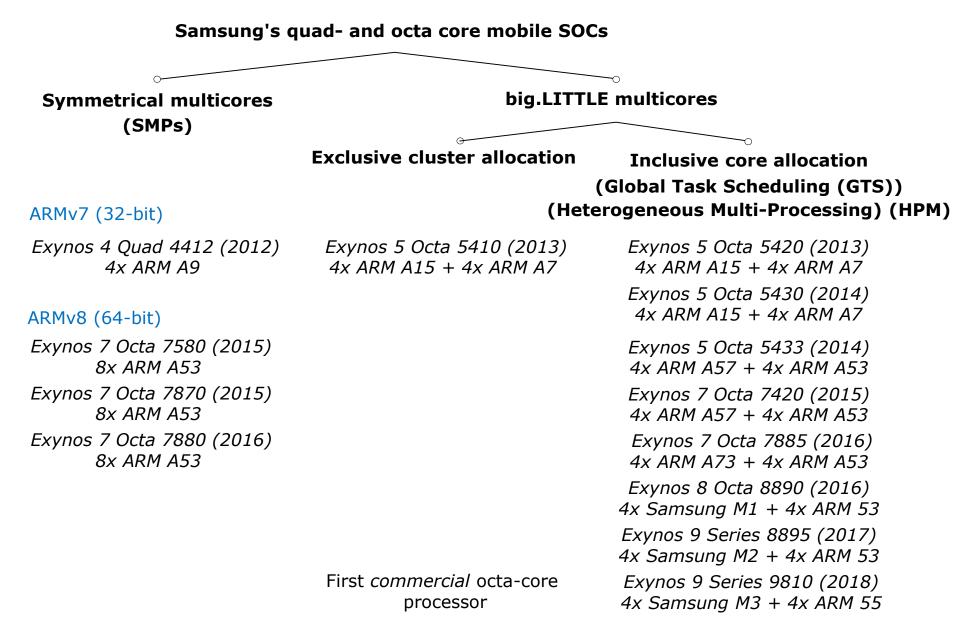

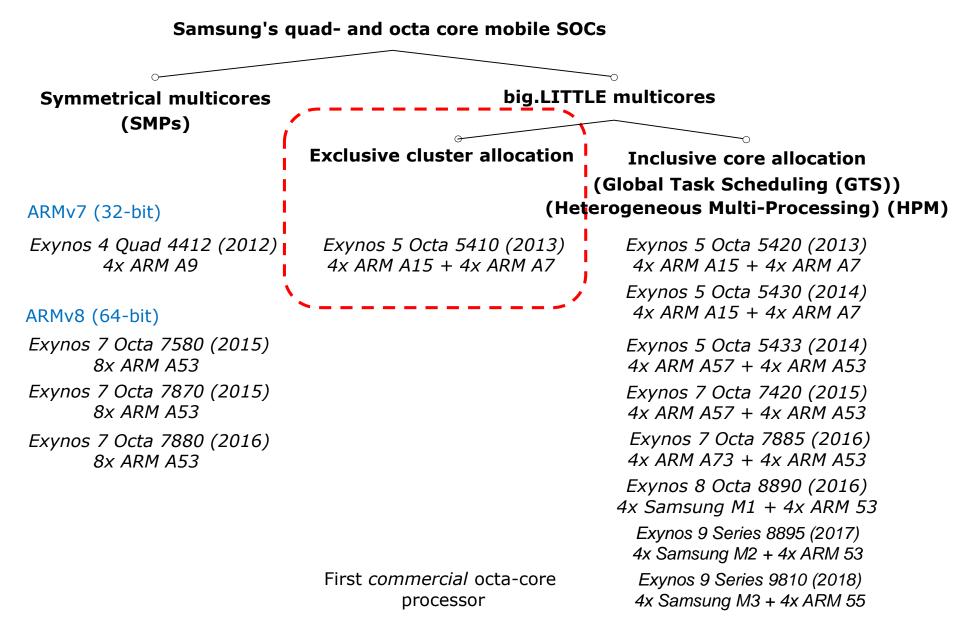

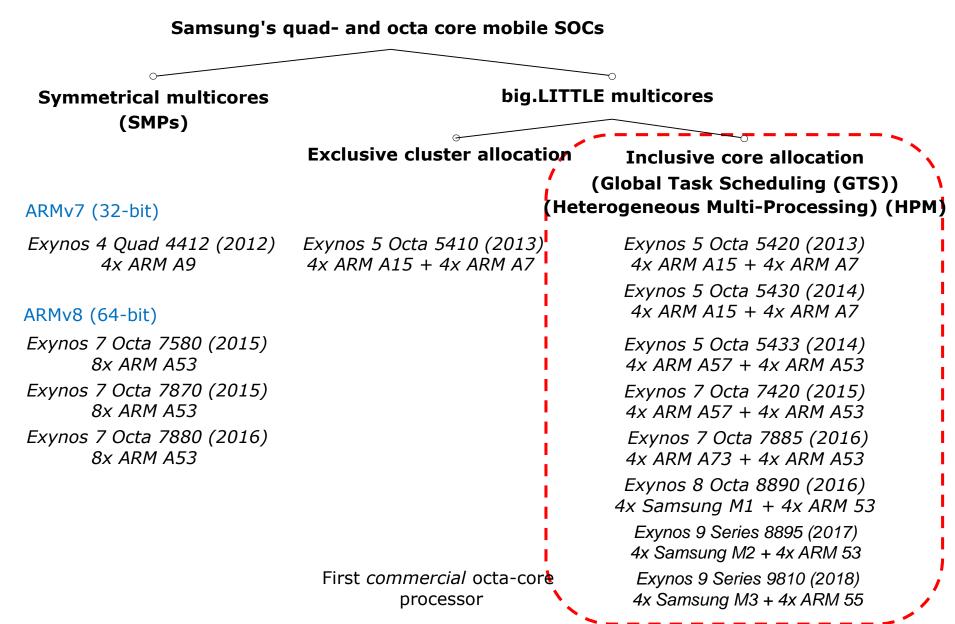

2. Overview of Samsung's quad- and octa core mobile SOCs

#### 2. Overview of Samsung's quad- and octa core mobile SOCs

3. Quad- and octa core SMPs

3. Quad- and octa core SMPs (1)

#### 3. Quad- and octa core SMPs

#### Main features of Samsung's quad- and octa core SMPs

| SoC                                   |                 |               | CPU        |       |             |                                                   |                                                       |                   |                                              |

|---------------------------------------|-----------------|---------------|------------|-------|-------------|---------------------------------------------------|-------------------------------------------------------|-------------------|----------------------------------------------|

| Model number                          | fab             | Instr.<br>set | Microarch. | cores | fc<br>(GHz) | GPU                                               | Memory<br>technology                                  | Availa-<br>bility | Utilizing devices<br>(examples)              |

| Exynos 4 Quad<br><i>(Exynos 4412)</i> | 32 nm<br>HKMG   | ARM<br>v7     | Cortex-A9  | 4     | 1.4         | ARM Mali-T400<br>MP4 @ 440 MHz;<br>15.8 GFLOPS    | 32-bit DCh.<br>DDR3-800<br>LPDDR3-800<br>(6.4 GB/sec) | 2012              | Samsung Galaxy SIII<br>Samsung Galaxy Note 2 |

| Exynos 7 Octa<br>(Exynos 7580)        | 20 nm<br>FinFET | ARM<br>v8-A   | Cortex-A53 | 8     | 1.5         | Mali-T720 MP2 @<br>668 MHz; 34<br>GFLOPS (FP16)   | 32-bits DCh.<br>LPDDR3-1866<br>(14.9 GB/s)            | Q2<br>2015        | Samsung Galaxy A5/<br>Samsung Galaxy A7      |

| Exynos 7 Octa<br>(Exynos 7870)        | 14 nm<br>FinFET | ARM<br>v8-A   | Cortex-A53 | 8     | 1.7         | Mali-T830 MP2 @<br>700 MHz; 47.6<br>GFLOPS (FP16) | 32-bits DCh.<br>LPDDR3-1866<br>(14.9 GB/s)            | Q1<br>2016        | Samsung Galaxy Tab A                         |

| Exynos 7 Octa<br>(Exynos 7880)        | 14 nm<br>FinFET | ARM<br>v8-A   | Cortex-A53 | 8     | 1.9         | Mali-T830 MP3                                     | 32-bits DCh.<br>LPDDR4x                               | 2016              | Samsung Galaxy A5/<br>Samsung Galaxy A7      |

3. Quad- and octa core SMPs (3)

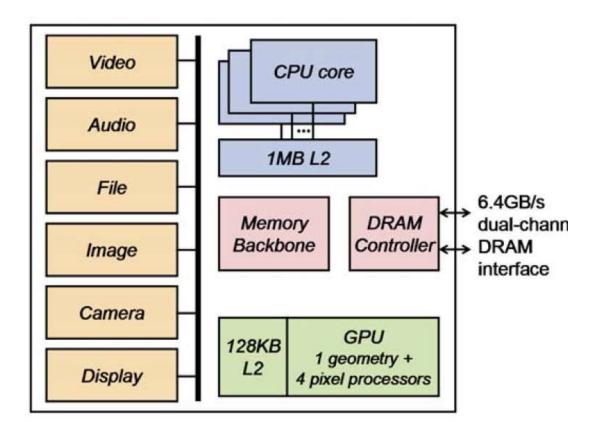

# Example: Samsung Exynos 4412 4-core SMP (2012) Architecture block diagram

## Power management of the Exynos 4 Quad (4412) (2012)

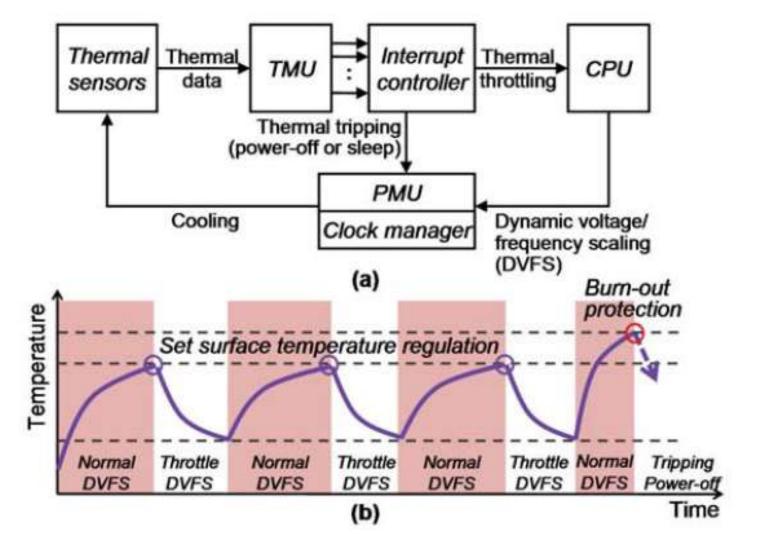

- It has a platform level power management unit, called the PMU.

- There are four power planes:

two for the CPUs, one for the GPU and one for the DRAM controller and the other functional blocks.

Per-core DVFS is implemented [63].

- Power gating is used for each core and all major functional units.

- There is also a separate thermal management unit (TMU).

- See the subsequent slide for an illustration of power and thermal management.

Power and thermal management of Samsung's Exynos 4412 (2012) [1]

PMU: Power Management Unit

TMU: Thermal Management Unit

# 4. Octa core big.LITTLE mobile SOCs with exclusive cluster allocation

4. Octa core big.LITTLE mobile SOC with exclusive cluster allocation (1)

4. Octa core big.LITTLE mobile SOCs with exclusive cluster allocation

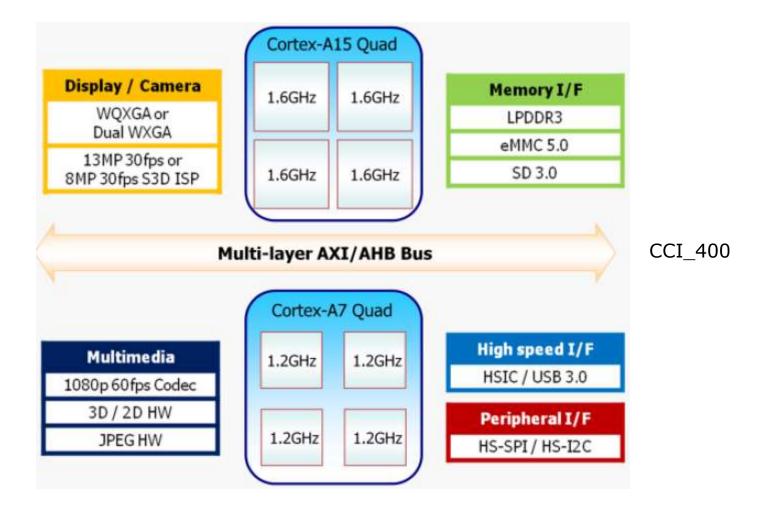

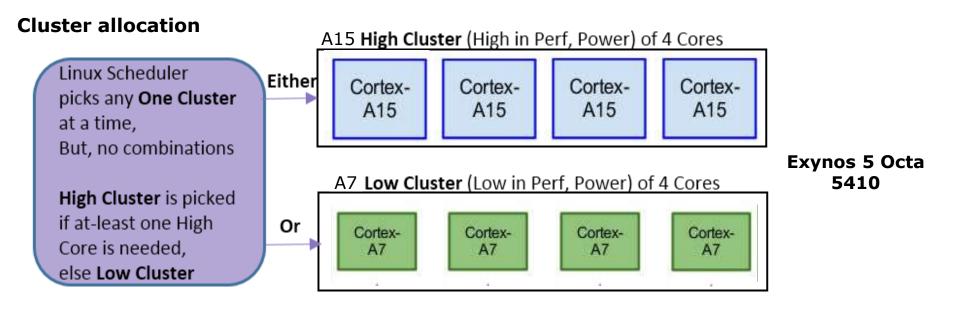

The world's first octa core mobile processor: Samsungs's Exynos Octa 5410 (2013) [2]

- It implements the 32-bit ARMv7 ISA.

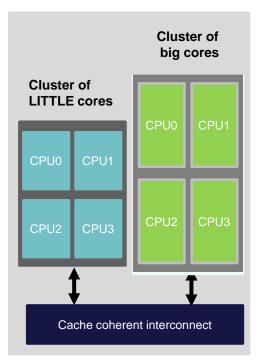

- It operates in the big.LITTLE configuration with cluster allocation for scheduling.

- Announced in 11/2012, launched in Galaxy S4 models in 4/2013.

#### 4. Octa core big.LITTLE mobile SOC with exclusive cluster allocation (3)

# Main features of Samsung's Exynos 5410 octa core big.LITTLE mobile SOC with exclusive cluster allocation

| SoC                            |                  | CPU           |                              |       |             |                                                   |                                            |                   |                                                   |

|--------------------------------|------------------|---------------|------------------------------|-------|-------------|---------------------------------------------------|--------------------------------------------|-------------------|---------------------------------------------------|

| Model number                   | fab.             | Instr.<br>set | Microarch.                   | cores | fc<br>(GHz) | GPU                                               | Memory<br>technology                       | Availa-<br>bility | Utilized in the devices<br>(examples)             |

| Exynos 5 Octa<br>(Exynos 5410) | 28<br>nm<br>HKMG | ARM<br>v7     | Cortex-<br>A15+<br>Cortex-A7 | 4+4   | 1.8<br>1.2  | IT PowerVR<br>SGX544MP3 @<br>480 MHz<br>49 GFLOPS | 32-bit DCh<br>LPDDR3-1600<br>(12.8 GB/sec) | Q2<br>2013        | Samsung Galaxy S4<br>I9500, ZTE Grand S II<br>TD, |

4. Octa core big.LITTLE mobile SOC with exclusive cluster allocation (4)

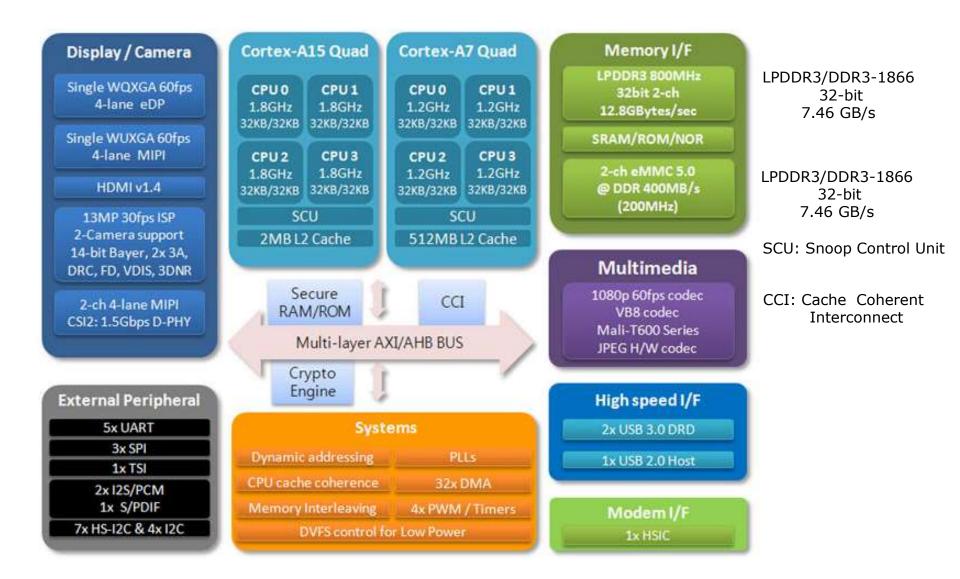

#### Block diagram of Samsung's Exynos 5 Octa 5410 [2]

4. Octa core big.LITTLE mobile SOC with exclusive cluster allocation (5)

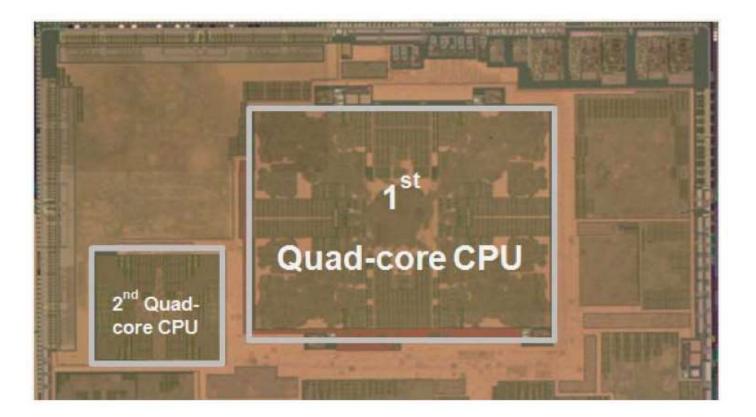

Assumed die photo of Samsung's Exynos 5 Octa 5410 [3]

Revealed at the International Solid-State Circuit Conference (ISSCC) in 2/2013 without specifying the chip designation [3].

#### 4. Octa core big.LITTLE mobile SOC with exclusive cluster allocation (6)

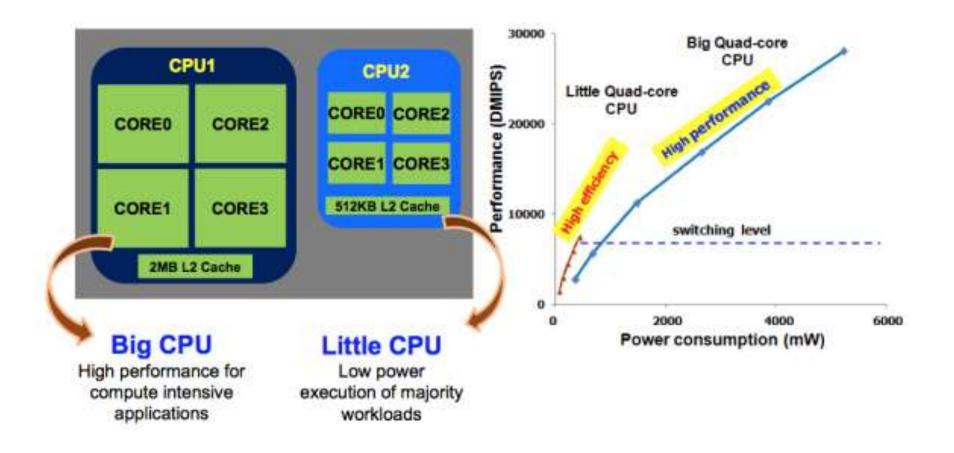

Principle of operation of the Exynos 5 Octa 5410 [3]

- For low performance demand the "Little CPU" and for higher performance demand the "Big CPU" is used.

- At a given switching level the scheduler performs a cluster switch.

4. Octa core big.LITTLE mobile SOC with exclusive cluster allocation (7)

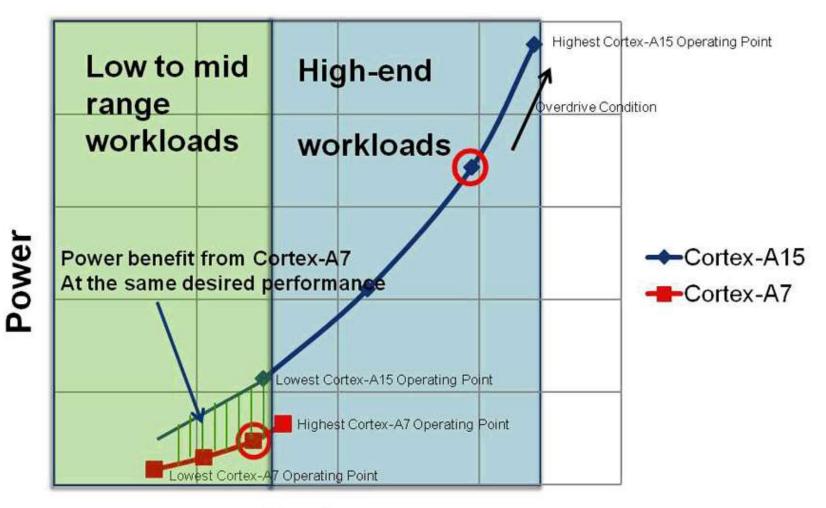

Performance points of operation of the LITTLE and big clusters [4]

# Performance

#### Remark

- In a White Paper [66] Samsung's engineers compare asynchronous architectures with per-core DVFS and synchronous big.LITTLE architectures concerning their energy efficiency.

- Their conclusion is that concerning the energy efficiency (e.g. power consumption performance) or net energy consumption the big.LITTLE architecture is superior vs. the per-core DVFS for the majority of commonly used applications, such as e-mail messaging, web browsing or multimedia playback.

- The reason is performance degradations due to cache misses or transferring data between different cores.

- Based on this finding Samsung implemented the big.LITTLE technology in the Exynos 5410 with synchronous DVFS (meaning that all cores within a cluster run at the same voltage and frequency).

4. Octa core big.LITTLE mobile SOC with exclusive cluster allocation (9)

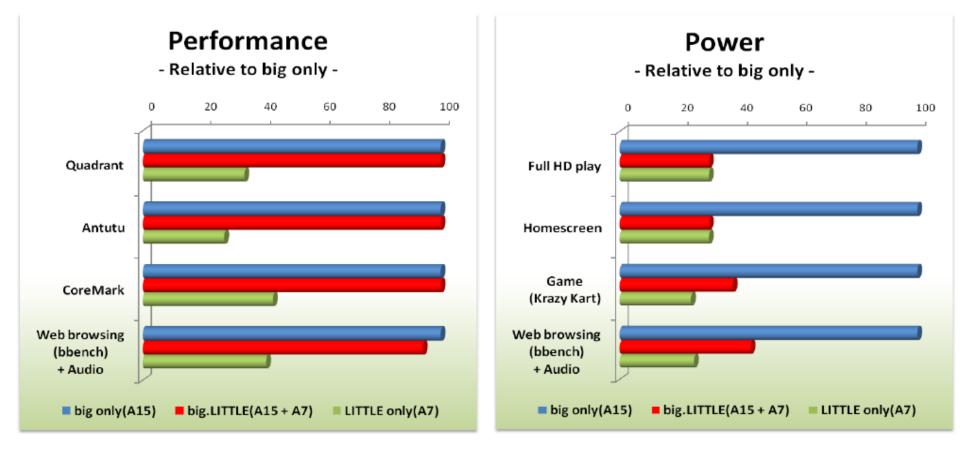

#### Performance and power results of the Exynos 5 Octa 5410 [2]

#### Remark

- According to sources there was a troublesome bug in the CCI-400 coherent bus interface [3].

- Thus, Samsung disabled the coherency between the two clusters, and as a consequence after cluster switches they need to invalidate all caches.

- Obviously, this has impeded performance and battery life.

#### 5. Octa core big.LITTLE mobile SOCs supporting GTS

5.1: Octa core big.LITTLE mobile SOCs supporting GTS -Overview

$\bullet$

- 5.2: The world's first octa core big.LITTLE mobile SOC supporting GTS: The Exynos 5 Octa 5420 (2013)

- 5.3: Samsung's first 64-bit octa core big.LITTLE SOC supporting GTS and operating in the ARMv8 Aarch32 mode: the Exynos 7 Octa 5433 (2014)

- 5.4: Samsung's first 64-bit octa core big.LITTLE SOC operating in the ARMv8 AArch64 mode: the Exynos 7 Octa 7420 (2015)

- 5.5: Samsung's first SoC including an in-house designed CPU core (the M1): the Exynos 8 Octa 8890 (2016)

- 5.6: Samsung's first 10 nm SOC: the Exynos 9 8895 (2017)

- 5.7: Samsung's first SOC supporting the DynamIQ cluster technology: the Exynos 9 9810 (2018)

# 5.1 Octa core big.LITTLE mobile SOCs supporting GTS - Overview

5.1 Octa core big.LITTLE mobile SOCs supporting GTS - Overview (1)

#### 5.1 Octa core big.LITTLE mobile SOCs supporting GTS – Overview

5.1 Octa core big.LITTLE mobile SOCs supporting GTS - Overview (2)

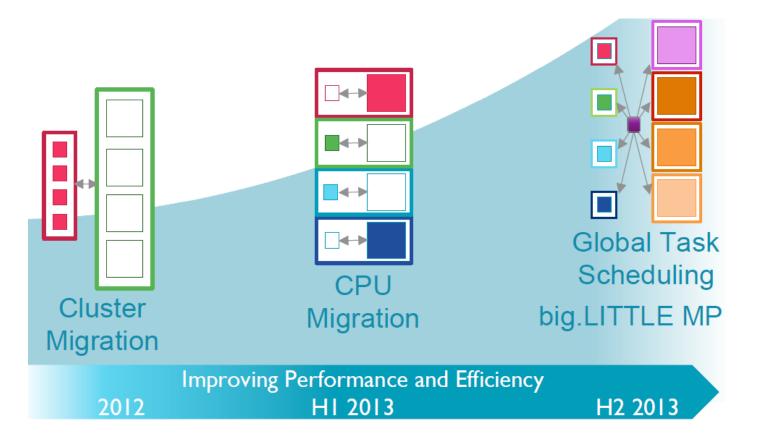

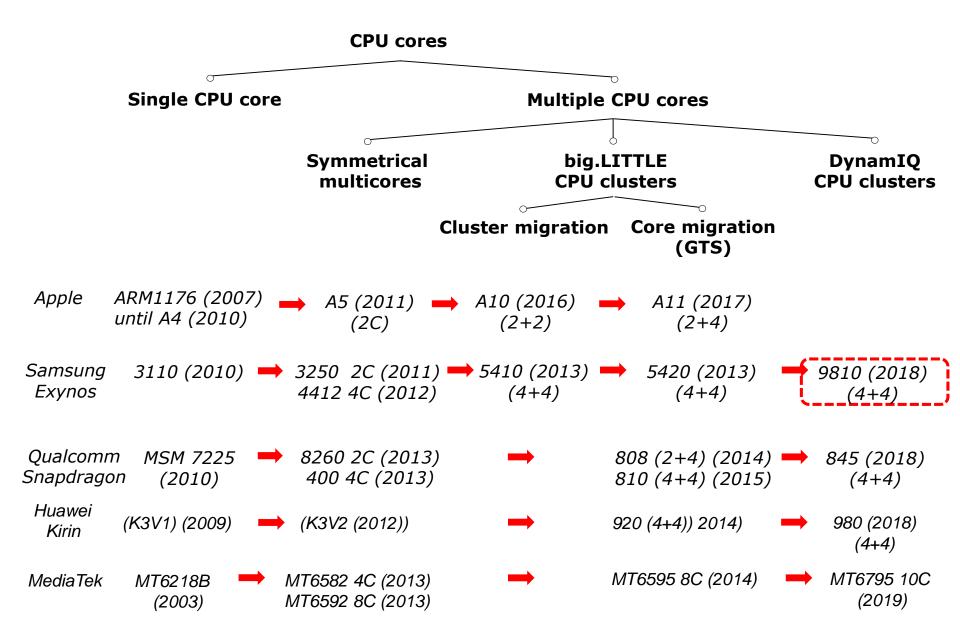

Evolution of the scheduling techniques [5]

#### Remark

- In CPU allocation there are big.LITTLE core pairs and the scheduler can activate either the big or the LITTLE core from each core pair.

- No commercial implementation is known using the CPU allocation.

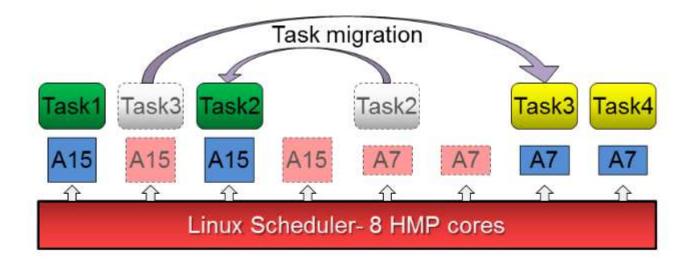

# Example for Global Task Scheduling (GTS) [72]

#### 5.1 Octa core big.LITTLE mobile SOCs supporting GTS - Overview (4)

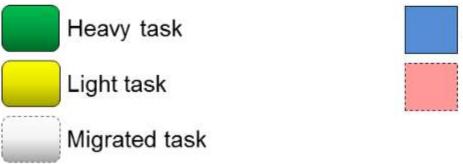

Benefits of GTS scheduling (designated as big.LITTLE MP in the Figure below) vs. exclusive cluster allocation [6]

Delivers higher power efficiency

Extends battery life

9

Improves user experience

## Overview of early big.LITTLE implementations supporting GTS

| Model                      | Year | Cores                                | Techn.         | Integrated<br>modem |

|----------------------------|------|--------------------------------------|----------------|---------------------|

| Samsung Exynos 5 Octa 5420 | 2013 | 4x A7 + 4x A15                       | 28 nm          | no                  |

| Samsung Exynos 5 Octa 5422 | 2014 | 4x A7 + 4x A15                       | 28 nm          | no                  |

| Samsung Exynos 5 Hexa 5260 | 2014 | 4x A7 + 2x A15                       | 28 nm          | no                  |

| Samsung Exynos 5 Octa 5430 | 2014 | 4x A7 + 4x A15                       | 20 nm          | no                  |

| Samsung Exynos 7 Octa 5433 | 2014 | 4x A53 + 4x A57                      | 20 nm          | no                  |

| Samsung Exynos 7 Octa 7420 | 2015 | 4x A53 + 4x A57                      | 14 nm          | no                  |

| Samsung Exynos 8 Octa 8890 | 2015 | 4x A53 + 4x M1                       | 14 nm          | yes                 |

| Qualcomm Snapdagon S 808   | 2014 | 4x A53 + 2x A57                      | 20 nm          | no                  |

| Qualcomm Snapdagon S 810   | 2015 | 4x A53 + 4x A57                      | 20 nm          | no                  |

| Qualcomm Snapdagon S 820   | 2016 | 2x Kryo 1.7 GHz +<br>2x Kryo 2.2 GHz | 14 nm<br>FnFET | no                  |

| MediaTek MT8135            | 2013 | 2x A7 + 2x A15                       | 28 nm          | no                  |

| MediaTek MT6595            | 2014 | 4x A7 + 4x A17                       | 28 nm          | yes                 |

| MediaTek MT6797            | 2015 | 8x A53+ 2x A57                       | 20 nm          | yes                 |

| Renesas MP 6530            | 2013 | 2x A7 + 2x A15                       | 28 nm          | yes                 |

| Allwinner UltraOcta A80    | 2014 | 4x A7 + 4x A15                       | 28 nm          | no                  |

#### 5.1 Octa core big.LITTLE mobile SOCs supporting GTS - Overview (6)

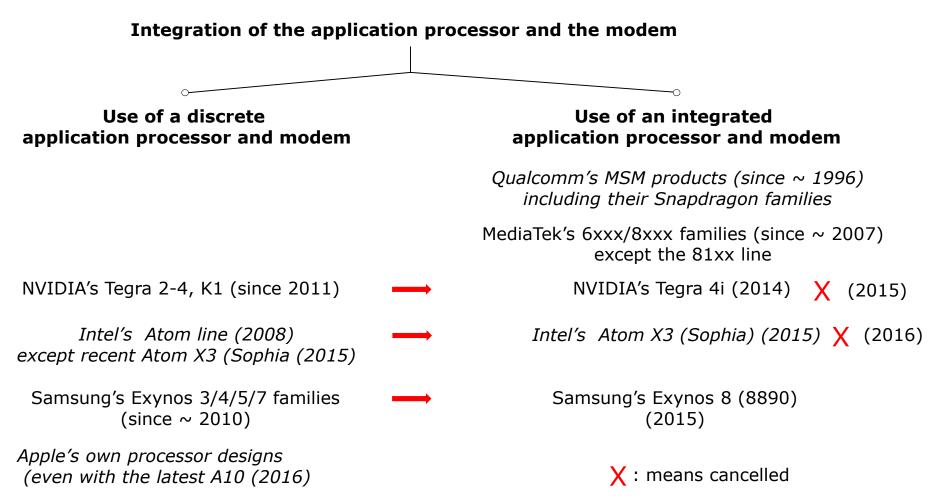

Integration of the application processor and the modem

- Integrating the modem into the chip results in less costs and shorter time to market.

- Qualcomm pioneered this move by designing integrated parts already about 1996.

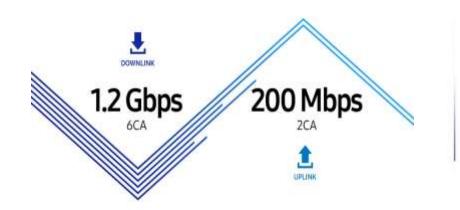

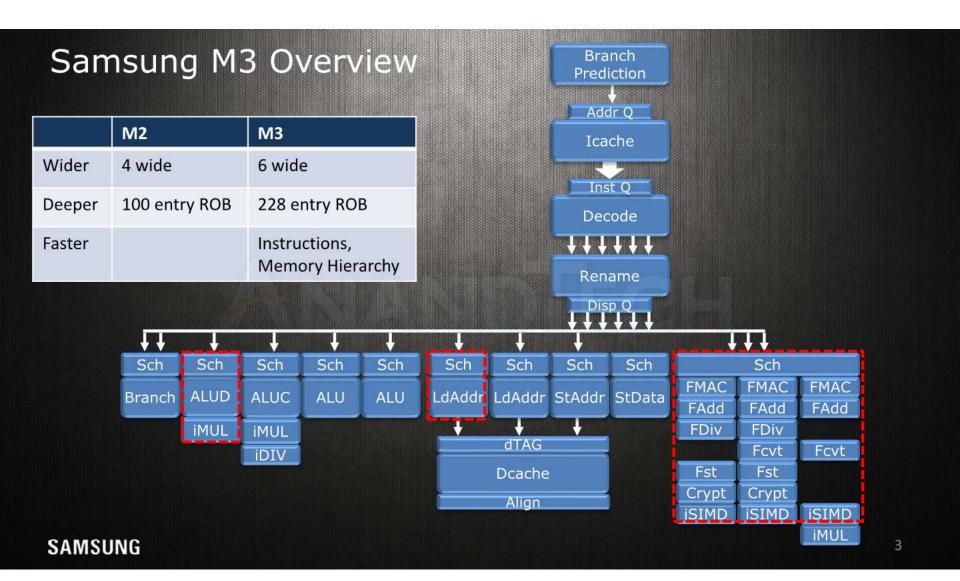

#### Main features of the Exynos 9810 vs. the Exynos 8995 [68]

| Samsung Exynos SoCs Specifications |                                                       |                                                   |  |  |  |  |  |  |  |  |

|------------------------------------|-------------------------------------------------------|---------------------------------------------------|--|--|--|--|--|--|--|--|

| SoC                                | Exynos 9810                                           | Exynos 8895                                       |  |  |  |  |  |  |  |  |

|                                    | 4x Exynos M3 @ 2.9 GHz<br>4x 512KB L2 ??              | 4x Exynos M2 @ 2.314 GHz<br>2048KB L2             |  |  |  |  |  |  |  |  |

| CPU                                | 4x Cortex A55 @ 1.9 GHz<br>4x 128KB L2                | 4x Cortex A53 @ 1.690GHz<br>512KB L2              |  |  |  |  |  |  |  |  |

|                                    | 4096KB L3 DSU ??                                      |                                                   |  |  |  |  |  |  |  |  |

| GPU                                | Mali G72MP18                                          | Mali G71MP20<br>@ 546MHz                          |  |  |  |  |  |  |  |  |

| Memory<br>Controller               | 4x 16-bit CH<br>LPDDR4x @ 1794MHz                     | 4x 16-bit CH<br>LPDDR4x @ 1794MHz<br>28.7GB/s B/W |  |  |  |  |  |  |  |  |

| Media                              | 10bit 4K120 encode & decode<br>H.265/HEVC, H.264, VP9 | 4K120 encode & decode<br>H.265/HEVC, H.264, VP9   |  |  |  |  |  |  |  |  |

|                                    | Shannon Integrated LTE<br>(Category 18/13)            | Shannon 355 Integrated LTE<br>(Category 16/13)    |  |  |  |  |  |  |  |  |

| Modem                              | DL = 1200 Mbps<br>6x20MHz CA, 256-QAM                 | DL = 1050 Mbps<br>5x20MHz CA, 256-QAM             |  |  |  |  |  |  |  |  |

|                                    | UL = 200 Mbps<br>2x20MHz CA, 256-QAM                  | UL = 150 Mbps<br>2x20MHz CA, 64-QAM               |  |  |  |  |  |  |  |  |

| ISP                                | Rear: 24MP<br>Front: 24MP<br>Dual: 16MP+16MP          | Rear: 28MP<br>Front: 28MP                         |  |  |  |  |  |  |  |  |

| Mfc.<br>Process                    | Samsung 10nm LPP                                      | Samsung 10nm LPE                                  |  |  |  |  |  |  |  |  |

# 5.1 Octa core big.LITTLE mobile SOCs supporting GTS - Overview (7)

#### Main features of Samsung's octa core big.LITTLE SOCs supporting GTS

| SoC                                   |                 | CPU           |                              |                |                    |                                                     | Memory                                            | Availa        | Utilizing devices                                                                                                   |  |

|---------------------------------------|-----------------|---------------|------------------------------|----------------|--------------------|-----------------------------------------------------|---------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------|--|

| Model number                          | fab             | Instr.<br>set | Cores                        | No of<br>cores | fc<br>(GHz)        | GPU                                                 | technology                                        | bility        | (examples)                                                                                                          |  |

| Exynos 5 Octa<br>(Exynos 5420)        | 28 nm<br>HKMG   |               | Cortex-A15+<br>Cortex-A7     | 4+4            | 1.8-1.9<br>1.2-1.3 | ARM Mali-T628<br>MP6 @ 533 MHz;<br>109 GFLOPS       | 32-bit DCh<br>LPDDR3e-1866<br>(14.9 GB/sec)       | Q3<br>2013    | Samsung Chromebook 2<br>11.6", Samsung Galaxy<br>Note 3/Note 10.1/Note Pro<br>12.2, Samsung Galaxy Tab<br>Pro/Tab S |  |

| Exynos 5 Octa<br>(Exynos 5422)        | 28 nm<br>HKMG   | ARM<br>v7     | Cortex-A15+<br>Cortex-A7     | 4+4            | 1.9-2.1<br>1.3-1.5 | ARM Mali-T628<br>MP6 @ 533 MHz<br>109 GFOPS         | 32-bit DCh<br>LPDDR3/DDR3-<br>1866 (14.9 GB/sec)  | Q2<br>2014    | Samsung Galaxy S5<br>(SM-G900H)                                                                                     |  |

| Exynos 5 Octa<br><i>(Exynos 5800)</i> | 28 nm<br>HKMG   |               | Cortex-A15+<br>Cortex-A7     | 4+4            | 2.1<br>1.3         | ARM Mali-T628<br>MP6 @ 533 MHz<br>109 GFLOPS        | 32-bit DCh<br>LPDDR3/DDR3-<br>1866 (14.9 GB/sec)  | Q2<br>2014    | Samsung Chromebook 2<br>13,3"                                                                                       |  |

| Exynos 5 Octa<br>(Exynos 5430)        | 20 nm<br>HKMG   |               | Cortex-A15+<br>Cortex-A7     | 4+4            | 1.8-2.0<br>1.3-1.5 | ARM Mali-T628<br>MP6 @ 600 MHz;<br>122 GFLOPS       | 32-bit DCh<br>LPDDR3e/DDR3-<br>2132 (17.0 GB/sec) | Q3<br>2014    | Samsung Galaxy Alpha<br>(SM-G850F)                                                                                  |  |

| Exynos 7 Octa<br>(Exynos 5433         | 20 nm<br>HKMG   |               | Cortex-A57+<br>Cortex-A53    | 4+4            | 1.9<br>1.3         | Mali-T760 MP6 @<br>700 MHz; 206<br>GFLOPS (FP16)    | 32-bits DCh<br>LPDDR3-1650<br>(13.2 GB/s)         | Q3/Q4<br>2014 | Samsung Galaxy Note 4<br>(SM-N910C)                                                                                 |  |

| Exynos 7 Octa<br>(Exynos 7420)        | 14 nm<br>FinFET |               | Cortex-A57+<br>Cortex-A53    | 4+4            | 2.1<br>1.5         | Mali-T760 MP8 @<br>772 MHz; 227<br>GFLOPS (FP16)    | 32-bits DCh<br>LPDDR4-3104<br>(24.9 GB/s)         | Q2<br>2015    | Samsung Galaxy S6<br>S6 Edge                                                                                        |  |

| Exynos 7 Octa<br>(Exynos 7885)        | 14 nm<br>HKMG   | ARM           | Cortex-A73+<br>Cortex-A53    | 4+4            | 2.2<br>1.6         | Mali-G71 MP2                                        | 32-bits DCh<br>LPDDR4x                            | Q1<br>2016    | Samsung Galaxy A8                                                                                                   |  |

| Exynos 8 Octa<br>(Exynos 8890)        | 14 nm<br>FinFET | v8-A          | Samsung<br>M1+<br>Cortex-A53 | 4+4            | 2.6-2.3<br>1.6     | Mali-T880 MP12 @<br>650 MHz; 265.2<br>GFLOPS (FP16) | 32-bits DCh<br>LPDDR4-3588<br>(28.7 GB/s)         | Q1<br>2016    | Samsung Galaxy S7<br>Samsung Galaxy S7 Edge                                                                         |  |

| Exynos 9 Series<br>(Exynos 8895)      | 10 nm<br>FinFET |               | Samsung<br>M2+<br>Cortex-A53 | 4+4            | 2.5<br>1.7         | Mali-G71 MP20                                       | 32-bits DCh?<br>LPDDR4x                           | Q2<br>2017    | Samsung Galaxy S8<br>Samsung Galaxy S8 Plus                                                                         |  |

| Exynos 9 Series<br>(Exynos 9810)      | 10 nm<br>FinFET |               | Samsung<br>M3+<br>Cortex-A55 | 4+4            | 2.9<br>1.9         | Mali-G72 MP18                                       | 32-bits DCh?<br>LPDDR4x                           | Q1<br>2018    | Samsung Galaxy S9<br>Samsung Galaxy S9 Plus                                                                         |  |

# OS support for GTS

- big.LITTLE technology needs suitable OS support for scheduling tasks to the right computing resources to achieve the least possible power consumption.

- ARM and Linaro jointly develop OS support fo GTS, these become available first as Linux or Android patch sets, later also they will be included into the mainstream Linux or - Android kernels.

- As an example, ARM/Linaro's IPA (Intelligent Power Management) became first available as a Linaro patch set in 09/2014 and then it was included into Linux 4.10 in 8/2015.

- It is stated that "software represents the Achilles' heel of the technology and severely limits its potential [57].

- In the Chapter on big-LITTLE processing we give an overview of the OS support of GTS.

#### Remark

Linaro is a non-profit foundation of interested firms to foster open source Linux packages that are optimized for ARM architectures.

#### Overview of OS kernels supporting GTS (announced or used)

| ARM/Linaro |                                                                        |                                                           | cation)                                                                                               | ARM/Linaro EAS<br>(Energy Aware Scheduling)<br>(on Google Pixel Phone), (10/2016)<br>14) |             |  |  |  |

|------------|------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------|--|--|--|

| MediaTek   | MediaTek CorePilot<br>(on MT8135)<br>(07/2013)                         | 1.0 (on Heli<br>(<br>Me                                   | ek CorePilot 2.0<br>o X10 (MT6595)<br>03/2015)<br>diaTek CorePilot 3<br>Helio X20 (MT679<br>(05/2015) |                                                                                          | ) (MT6799)) |  |  |  |

| Qualcomm   | Energy Aw<br>(on Snapdr                                                | alcomm's<br>vare Scheduling<br>agoon 610/615)<br>2/2014)) | , , , ,                                                                                               | em Manager<br>oon 820)                                                                   |             |  |  |  |

| Samsung    | Samsung's big.LIT<br>(≈ARM's big.LITTI<br>(on Exynos 5 mo<br>(09/2013) | 1                                                         |                                                                                                       |                                                                                          |             |  |  |  |

|            | 2013                                                                   | 2014                                                      | 2015                                                                                                  | 2016                                                                                     | 2017        |  |  |  |

5.2: The world's first octa core big.LITTLE mobile SOC supporting GTS: Samsungs's Exynos 5 Octa 5420 (2013)

- 5.2: The world's first octa core big.LITTLE mobile SOC supporting GTS: Samsungs's Exynos 5 Octa 5420 (2013) [2]

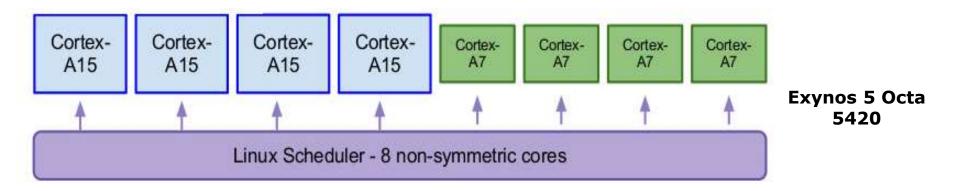

- It is a 32-bit ARMv7 mobile processor.

- Announced in 03/2013, launched in Galaxy S4 models in 4/2013.

- Task scheduling supports GTS, called HMP (Heterogeneous Multi-Processing) by Samsung.

# 5.2 The Exynos 5 Octa 5420 (2)

## Main features of Samsung's Exynos 5 Octa 5420 (2013)

| SoC                                    |                 | CPU           |                              |                |                    |                                                     | Memory                                            | Availa        | Utilizing devices                                                                                                   |

|----------------------------------------|-----------------|---------------|------------------------------|----------------|--------------------|-----------------------------------------------------|---------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------|

| Model number                           | fab             | Instr.<br>set | Cores                        | No of<br>cores | fc<br>(GHz)        | GPU                                                 | technology                                        | bility        | (examples)                                                                                                          |

| Exynos 5 Octa<br>( <i>Exynos 5420)</i> | 28 nm<br>HKMG   |               | Cortex-A15+<br>Cortex-A7     | 4+4            | 1.8-1.9<br>1.2-1.3 | ARM Mali-T628<br>MP6 @ 533 MHz;<br>109 GFLOPS       | 32-bit DCh<br>LPDDR3e-1866<br>(14.9 GB/sec)       | Q3<br>2013    | Samsung Chromebook 2<br>11.6", Samsung Galaxy<br>Note 3/Note 10.1/Note Pro<br>12.2, Samsung Galaxy Tab<br>Pro/Tab S |

| Exynos 5 Octa<br>(Exynos 5422)         | 28 nm<br>HKMG   | ARM<br>v7     | Cortex-A15+<br>Cortex-A7     | 4+4            | 1.9-2.1<br>1.3-1.5 | ARM Mali-T628<br>MP6 @ 533 MHz<br>109 GFOPS         | 32-bit DCh<br>LPDDR3/DDR3-<br>1866 (14.9 GB/sec)  | Q2<br>2014    | Samsung Galaxy S5<br>(SM-G900H)                                                                                     |

| Exynos 5 Octa<br>(Exynos 5800)         | 28 nm<br>HKMG   |               | Cortex-A15+<br>Cortex-A7     | 4+4            | 2.1<br>1.3         | ARM Mali-T628<br>MP6 @ 533 MHz<br>109 GFLOPS        | 32-bit DCh<br>LPDDR3/DDR3-<br>1866 (14.9 GB/sec)  | Q2<br>2014    | Samsung Chromebook 2<br>13,3"                                                                                       |

| Exynos 5 Octa<br>(Exynos 5430)         | 20 nm<br>HKMG   |               | Cortex-A15+<br>Cortex-A7     | 4+4            | 1.8-2.0<br>1.3-1.5 | ARM Mali-T628<br>MP6 @ 600 MHz;<br>122 GFLOPS       | 32-bit DCh<br>LPDDR3e/DDR3-<br>2132 (17.0 GB/sec) | Q3<br>2014    | Samsung Galaxy Alpha<br>(SM-G850F)                                                                                  |

| Exynos 7 Octa<br>(Exynos 5433          | 20 nm<br>HKMG   |               | Cortex-A57+<br>Cortex-A53    | 4+4            | 1.9<br>1.3         | Mali-T760 MP6 @<br>700 MHz; 206<br>GFLOPS (FP16)    | 32-bits DCh<br>LPDDR3-1650<br>(13.2 GB/s)         | Q3/Q4<br>2014 | Samsung Galaxy Note 4<br>(SM-N910C)                                                                                 |

| Exynos 7 Octa<br>(Exynos 7420)         | 14 nm<br>FinFET |               | Cortex-A57+<br>Cortex-A53    | 4+4            | 2.1<br>1.5         | Mali-T760 MP8 @<br>772 MHz; 227<br>GFLOPS (FP16)    | 32-bits DCh<br>LPDDR4-3104<br>(24.9 GB/s)         | Q2<br>2015    | Samsung Galaxy S6<br>S6 Edge                                                                                        |

| Exynos 7 Octa<br>(Exynos 7885)         | 14 nm<br>HKMG   |               | Cortex-A73+<br>Cortex-A53    | 4+4            | 2.2<br>1.6         | Mali-G71 MP2                                        | 32-bits DCh<br>LPDDR4x                            | Q1<br>2016    | Samsung Galaxy A8                                                                                                   |

| Exynos 8 Octa<br>(Exynos 8890)         | 14 nm<br>FinFET |               | Samsung<br>M1+<br>Cortex-A53 | 4+4            | 2.6-2.3<br>1.6     | Mali-T880 MP12 @<br>650 MHz; 265.2<br>GFLOPS (FP16) | 32-bits DCh<br>LPDDR4-3588<br>(28.7 GB/s)         | Q1<br>2016    | Samsung Galaxy S7<br>Samsung Galaxy S7 Edge                                                                         |

| Exynos 9 Series<br>(Exynos 8895)       | 10 nm<br>FinFET |               | Samsung<br>M2+<br>Cortex-A53 | 4+4            | 2.5<br>1.7         | Mali-G71 MP20                                       | 32-bits DCh?<br>LPDDR4x                           | Q2<br>2017    | Samsung Galaxy S8<br>Samsung Galaxy S8 Plus                                                                         |

| Exynos 9 Series<br>(Exynos 9810)       | 10 nm<br>FinFET |               | Samsung<br>M3+<br>Cortex-A55 | 4+4            | 2.9<br>1.9         | Mali-G72 MP18                                       | 32-bits DCh?<br>LPDDR4x                           | Q1<br>2018    | Samsung Galaxy S9<br>Samsung Galaxy S9 Plus                                                                         |

## 5.2 The Exynos 5 Octa 5420 (3)

## Block diagram of Samsung's Exynos 5 Octa 5420 [7]

# Contrasting GTS with exclusive cluster switching (Based on [8])

#### Heterogeneous Mult-Processing (HMP)

## 5.2 The Exynos 5 Octa 5420 (5)

## Remark [9]

- The 5420 was followed by the 5422, it is Samsung's second octa core big.LITTLE processor operating under GTS, announced in 2/2014, available in Q1 2014.

- It is basically a faster variant of the 5420, as seen in the next Figure.

#### 5.2 The Exynos 5 Octa 5420 (6)

# Block diagram of the Samsung Exynos 5 Octa 5422 [10]

# Samsung's subsequent big.LITTLE models supporting GTS

In 8/2014 Samsung announced their first 20 nm octa core big.LITTLE processor, the Exynos 5 Octa 5430 with 4 Cortex-A15 and 4 Cortex-A7 cores.

Due to the new low-power High-K Metal Gate (HKMG) process technology power consumption of this processor could be lowered by 28 % compared to the previous 28 nm technology [11].

About the same time Samsung unveiled also the Exynos 5 Octa 5433, that included 4 Cortex-A57 and 4 Cortex-A53 64-bit cores but runs in 32-bit mode (called AArch32 mode).

The Exynos 5 Octa 5433 incorporates the Mali T760 GPU that is claimed to offer 76 % more performance than the previous Mali T628

Later (in 10/2014) Samsung introduced the Exynos 7 Octa 7420 that included the same cores as the Exynos 5 Octa 5 5433 but runs already in 64-bit mode (AArch64).

Samsung announced about 57 % performance increase over the Exynos 5 Octa 5433 implementation [12].

• Subsequently, the Examples 2 and 3 give some more details about the Exynos 5 Octa 5433 and the Exynos 7 Octa 7420.

5.3: Samsung's first 64-bit octa core big.LITTLE mobile processor supporting GTS and operating in the ARMv8 Aarch32 mode: the Exynos 5 Octa 5433 (2014)

- 5.3: Samsung's first 64-bit octa core big.LITTLE SOC supporting GTS and operating in the ARMv8 Aarch32 mode: the Exynos 5 Octa 5433 (2014)

- The Exynos 5 Octa 5433 is Samsung's first mobile processor built up of ARMv8 cores, but it operates in the AARch32 execution mode [13].

This is the reason why the model designation starts with 5 instead of 7.

Nevertheless, it takes advantage in the architectural improvements of the Aarchv8 cores (actually the Cortex-A57 and Cortex-A53 cores), as indicated next in the performance ranking of this processor.

## Main features of Samsung's Exynos 5 Octa 5433 (2014)

| SoC                              |                 | CPU           |                              |                |                    |                                                     | Memory                                            | Availa        | Utilizing devices                                                                                                   |

|----------------------------------|-----------------|---------------|------------------------------|----------------|--------------------|-----------------------------------------------------|---------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------|

| Model number                     | fab             | Instr.<br>set | Cores                        | No of<br>cores | fc<br>(GHz)        | GPU                                                 | technology                                        | bility        | (examples)                                                                                                          |

| Exynos 5 Octa<br>(Exynos 5420)   | 28 nm<br>HKMG   |               | Cortex-A15+<br>Cortex-A7     | 4+4            | 1.8-1.9<br>1.2-1.3 | ARM Mali-T628<br>MP6 @ 533 MHz;<br>109 GFLOPS       | 32-bit DCh<br>LPDDR3e-1866<br>(14.9 GB/sec)       | Q3<br>2013    | Samsung Chromebook 2<br>11.6", Samsung Galaxy<br>Note 3/Note 10.1/Note Pro<br>12.2, Samsung Galaxy Tab<br>Pro/Tab S |

| Exynos 5 Octa<br>(Exynos 5422)   | 28 nm<br>HKMG   | ARM<br>v7     | Cortex-A15+<br>Cortex-A7     | 4+4            | 1.9-2.1<br>1.3-1.5 | ARM Mali-T628<br>MP6 @ 533 MHz<br>109 GFOPS         | 32-bit DCh<br>LPDDR3/DDR3-<br>1866 (14.9 GB/sec)  | Q2<br>2014    | Samsung Galaxy S5<br>(SM-G900H)                                                                                     |

| Exynos 5 Octa<br>(Exynos 5800)   | 28 nm<br>HKMG   |               | Cortex-A15+<br>Cortex-A7     | 4+4            | 2.1<br>1.3         | ARM Mali-T628<br>MP6 @ 533 MHz<br>109 GFLOPS        | 32-bit DCh<br>LPDDR3/DDR3-<br>1866 (14.9 GB/sec)  | Q2<br>2014    | Samsung Chromebook 2<br>13,3"                                                                                       |

| Exynos 5 Octa<br>(Exynos 5430)   | 20 nm<br>HKMG   |               | Cortex-A15+<br>Cortex-A7     | 4+4            | 1.8-2.0<br>1.3-1.5 | ARM Mali-T628<br>MP6 @ 600 MHz;<br>122 GFLOPS       | 32-bit DCh<br>LPDDR3e/DDR3-<br>2132 (17.0 GB/sec) | Q3<br>2014    | Samsung Galaxy Alpha<br>(SM-G850F)                                                                                  |

| Exynos 7 Octa<br>(Exynos 5433    | 20 nm<br>HKMG   |               | Cortex-A57+<br>Cortex-A53    | 4+4            | 1.9<br>1.3         | Mali-T760 MP6 @<br>700 MHz; 206<br>GELOPS (EP16)    | 32-bits DCh<br>LPDDR3-1650<br>(13.2 GB/s)         | Q3/Q4<br>2014 | Samsung Galaxy Note 4<br>(SM-N910C)                                                                                 |

| Exynos 7 Octa<br>(Exynos 7420)   | 14 nm<br>FinFET |               | Cortex-A57+<br>Cortex-A53    | 4+4            | 2.1<br>1.5         | Mali-T760 MP8 @<br>772 MHz; 227<br>GFLOPS (FP16)    | 32-bits DCh<br>LPDDR4-3104<br>(24.9 GB/s)         | Q2<br>2015    | Samsung Galaxy S6<br>S6 Edge                                                                                        |

| Exynos 7 Octa<br>(Exynos 7885)   | 148 nm<br>HKMG  | ARM           | Cortex-A73+<br>Cortex-A53    | 4+4            | 2.2<br>1.6         | Mali-G71 MP2                                        | 32-bits DCh<br>LPDDR4x                            | Q1<br>2016    | Samsung Galaxy A8                                                                                                   |

| Exynos 8 Octa<br>(Exynos 8890)   | 14 nm<br>FinFET | v8-A          | Samsung<br>M1+<br>Cortex-A53 | 4+4            | 2.6-2.3<br>1.6     | Mali-T880 MP12 @<br>650 MHz; 265.2<br>GFLOPS (FP16) | 32-bits DCh<br>LPDDR4-3588<br>(28.7 GB/s)         | Q1<br>2016    | Samsung Galaxy S7<br>Samsung Galaxy S7 Edge                                                                         |

| Exynos 9 Series<br>(Exynos 8895) | 10 nm<br>FinFET |               | Samsung<br>M2+<br>Cortex-A53 | 4+4            | 2.5<br>1.7         | Mali-G71 MP20                                       | 32-bits DCh?<br>LPDDR4x                           | Q2<br>2017    | Samsung Galaxy S8<br>Samsung Galaxy S8 Plus                                                                         |

| Exynos 9 Series<br>(Exynos 9810) | 10 nm<br>FinFET |               | Samsung<br>M3+<br>Cortex-A55 | 4+4            | 2.9<br>1.9         | Mali-G72 MP18                                       | 32-bits DCh?<br>LPDDR4x                           | Q1<br>2018    | Samsung Galaxy S9<br>Samsung Galaxy S9 Plus                                                                         |

#### 5.3 The Exynos 5 Octa 5433 (4)

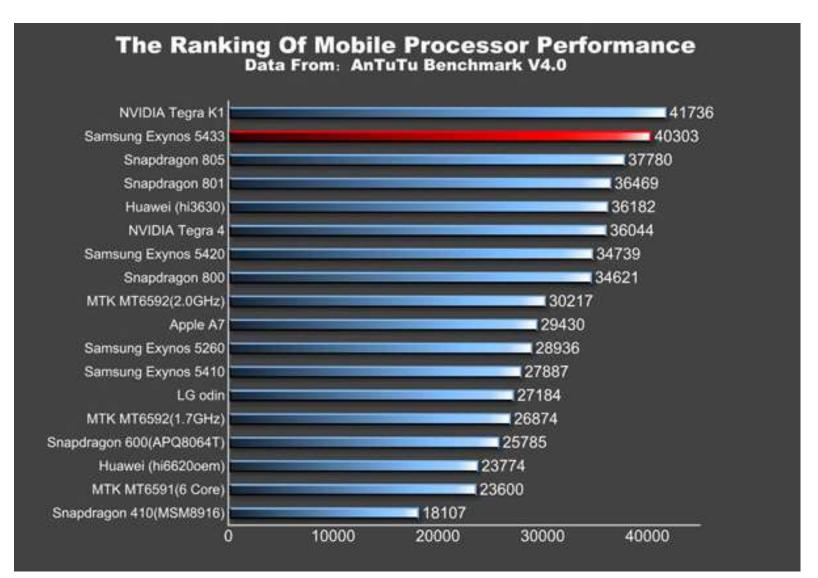

# Performance ranking of the Exynos 7 Octa 5433 based on the AnTuTu v4.0 benchmark [14]

# Main features of Samsung's Exynos 5 Octa SOCs [13]

| Samsung Exynos 5 Octa 2014 lineup |                      |                      |                      |  |  |  |  |  |

|-----------------------------------|----------------------|----------------------|----------------------|--|--|--|--|--|

| SoC                               | Samsung              | Samsung              | Samsung              |  |  |  |  |  |

|                                   | Exynos 5422          | Exynos 5430          | Exynos 5433          |  |  |  |  |  |

| CPU                               | 4x Cortex A7 r0p5 @  | 4x Cortex A7 r0p5 @  | 4x Cortex A53 @      |  |  |  |  |  |

|                                   | 1.3GHz               | 1.3GHz               | 1.3GHz               |  |  |  |  |  |

|                                   | 4x Cortex A15 r2p4 @ | 4x Cortex A15 r3p3 @ | 4x Cortex A57 r1p0 @ |  |  |  |  |  |

|                                   | 1.9GHz               | 1.8GHz               | 1.9GHz               |  |  |  |  |  |

| Memory                            | 2x 32-bit @ 933MHz   | 2x 32-bit @ 1066MHz  | 2x 32-bit @ 825MHz   |  |  |  |  |  |

| Controller                        | 14.9GB/s b/w         | 17.0GB/s b/w         | 13.2GB/s b/w         |  |  |  |  |  |

| GPU                               | Mali T628MP6         | Mali T628MP6         | Mali T760MP <b>6</b> |  |  |  |  |  |

|                                   | @ 533MHz             | @ 600MHz             | @ 700MHz             |  |  |  |  |  |

| Mfc.                              | Samsung              | Samsung              | Samsung              |  |  |  |  |  |

| Process                           | 28nm HKMG            | 20nm HKMG            | 20nm HKMG            |  |  |  |  |  |

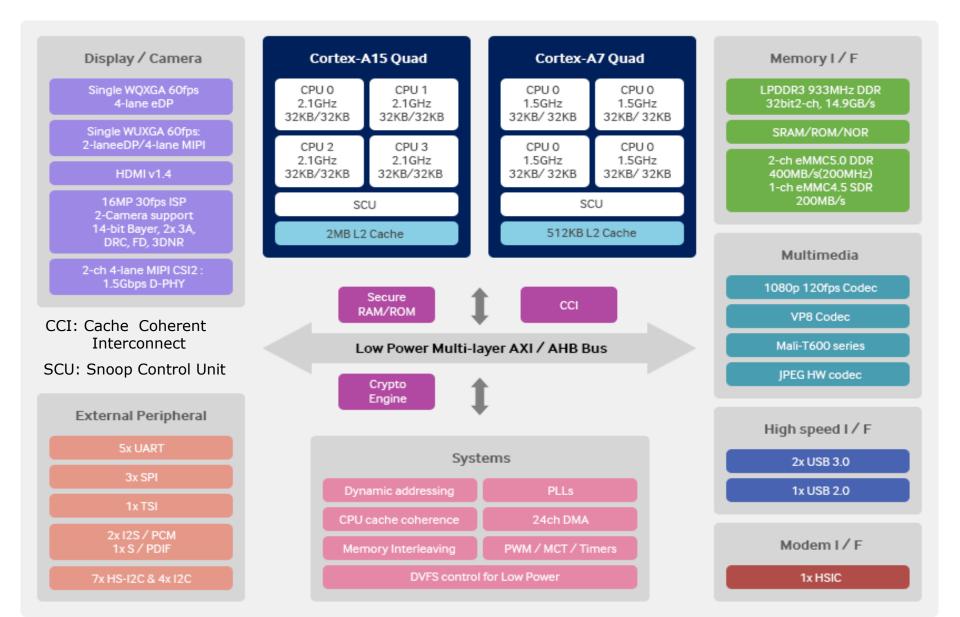

## Block diagram of Samsung's Exynos 5 Octa 5433 mobile processor [15]

5.4: Samsung's first 64-bit octa core big.LITTLE SOC operating in the ARMv8 AArch64 mode: the Exynos 7 Octa 7420 (2015)

- 5.4.1 The Exynos 7 Octa 7420 Overview

- 5.4.2 Introducing binning in form of ASV groups

5.4.3 Introducing AVS, called ASV

(Adaptive Scaling Voltage) by Samsung

- 5.4.4 Introducing LPDDR4

- 5.4.5 Implementing a hardware memory compressor

# 5.4.1: The Exynos 7 Octa 7420 - Overview

## 5.4.1: The Exynos 7 Octa 7420 - Overview

- The Exynos 7 Octa 7420 is the world's first 64-bit octa core big.LITTLE SOC operating in the ARMv8 AArch64 mode-

- It is the world's first application processor built on 14 nm FinFET.

- It is the core part of the Samsung Galaxy S6.

- The Exynos 7 Octa 7420 is the 14 nm shrink of the Exynos 5 5433 with major enhancements, such as ASV (Adaptive Scaling Voltage).

## Main features of Samsung's Exynos 7 Octa 7420 (2015)

| SoC                              |                 | CPU           |                              |                |                    |                                                     | Memory                                            | Availa        | Utilizing devices                                                                                                   |

|----------------------------------|-----------------|---------------|------------------------------|----------------|--------------------|-----------------------------------------------------|---------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------|

| Model number                     | fab             | Instr.<br>set | Cores                        | No of<br>cores | fc<br>(GHz)        | GPU                                                 | technology                                        | bility        | (examples)                                                                                                          |

| Exynos 5 Octa<br>(Exynos 5420)   | 28 nm<br>HKMG   |               | Cortex-A15+<br>Cortex-A7     | 4+4            | 1.8-1.9<br>1.2-1.3 | ARM Mali-T628<br>MP6 @ 533 MHz;<br>109 GFLOPS       | 32-bit DCh<br>LPDDR3e-1866<br>(14.9 GB/sec)       | Q3<br>2013    | Samsung Chromebook 2<br>11.6", Samsung Galaxy<br>Note 3/Note 10.1/Note Pro<br>12.2, Samsung Galaxy Tab<br>Pro/Tab S |

| Exynos 5 Octa<br>(Exynos 5422)   | 28 nm<br>HKMG   | ARM<br>v7     | Cortex-A15+<br>Cortex-A7     | 4+4            | 1.9-2.1<br>1.3-1.5 | ARM Mali-T628<br>MP6 @ 533 MHz<br>109 GFOPS         | 32-bit DCh<br>LPDDR3/DDR3-<br>1866 (14.9 GB/sec)  | Q2<br>2014    | Samsung Galaxy S5<br>(SM-G900H)                                                                                     |

| Exynos 5 Octa<br>(Exynos 5800)   | 28 nm<br>HKMG   |               | Cortex-A15+<br>Cortex-A7     | 4+4            | 2.1<br>1.3         | ARM Mali-T628<br>MP6 @ 533 MHz<br>109 GFLOPS        | 32-bit DCh<br>LPDDR3/DDR3-<br>1866 (14.9 GB/sec)  | Q2<br>2014    | Samsung Chromebook 2<br>13,3"                                                                                       |

| Exynos 5 Octa<br>(Exynos 5430)   | 20 nm<br>HKMG   |               | Cortex-A15+<br>Cortex-A7     | 4+4            | 1.8-2.0<br>1.3-1.5 | ARM Mali-T628<br>MP6 @ 600 MHz;<br>122 GFLOPS       | 32-bit DCh<br>LPDDR3e/DDR3-<br>2132 (17.0 GB/sec) | Q3<br>2014    | Samsung Galaxy Alpha<br>(SM-G850F)                                                                                  |

| Exynos 7 Octa<br>(Exynos 5433    | 20 nm<br>HKMG   |               | Cortex-A57+<br>Cortex-A53    | 4+4            | 1.9<br>1.3         | Mali-T760 MP6 @<br>700 MHz; 206<br>GFLOPS (FP16)    | 32-bits DCh<br>LPDDR3-1650<br>(13.2 GB/s)         | Q3/Q4<br>2014 | Samsung Galaxy Note 4<br>(SM-N910C)                                                                                 |

| Exynos 7 Octa<br>(Exynos 7420)   | 14 nm<br>FinFET |               | Cortex-A57+<br>Cortex-A53    | 4+4            | 2.1<br>1.5         | Mali-T760 MP8 @<br>772 MHz; 227<br>GFLOPS (FP16)    | 32-bits DCh<br>LPDDR4-3104<br>(24.9 GB/s)         | Q2<br>2015    | Samsung Galaxy S6<br>S6 Edge                                                                                        |

| Exynos 7 Octa<br>(Exynos 7885    | 14 nm<br>HKMG   | ARM           | Cortex-A73+<br>Cortex-A53    | 4+4            | 2.2<br>1.6         | Mali-G71 MP2                                        | 32-bits DCh<br>LPDDR4x                            | Q1<br>2016    | Samsung Galaxy A8                                                                                                   |

| Exynos 8 Octa<br>(Exynos 8890)   | 14 nm<br>FinFET | v8-A          | Samsung<br>M1+<br>Cortex-A53 | 4+4            | 2.6-2.3<br>1.6     | Mali-T880 MP12 @<br>650 MHz; 265.2<br>GFLOPS (FP16) | 32-bits DCh<br>LPDDR4-3588<br>(28.7 GB/s)         | Q1<br>2016    | Samsung Galaxy S7<br>Samsung Galaxy S7 Edge                                                                         |

| Exynos 9 Series<br>(Exynos 8895) | 10 nm<br>FinFET |               | Samsung<br>M2+<br>Cortex-A53 | 4+4            | 2.5<br>1.7         | Mali-G71 MP20                                       | 32-bits DCh?<br>LPDDR4x                           | Q2<br>2017    | Samsung Galaxy S8<br>Samsung Galaxy S8 Plus                                                                         |

| Exynos 9 Series<br>(Exynos 9810) | 10 nm<br>FinFET |               | Samsung<br>M3+<br>Cortex-A55 | 4+4            | 2.9<br>1.9         | Mali-G72 MP18                                       | 32-bits DCh?<br>LPDDR4x                           | Q1<br>2018    | Samsung Galaxy S9<br>Samsung Galaxy S9 Plus                                                                         |

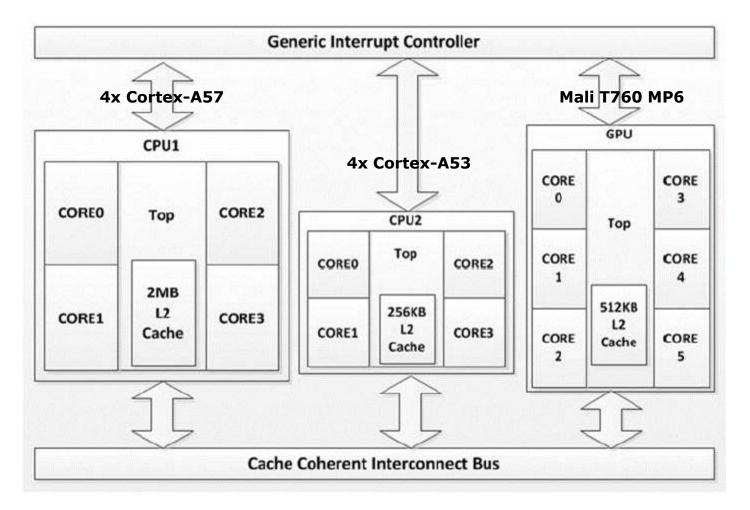

Assumed block diagram of Samsung's Exynos 7 Octa 7420 processor [16]

5.4.1 The Exynos 7 Octa 7420 - Overview (4)

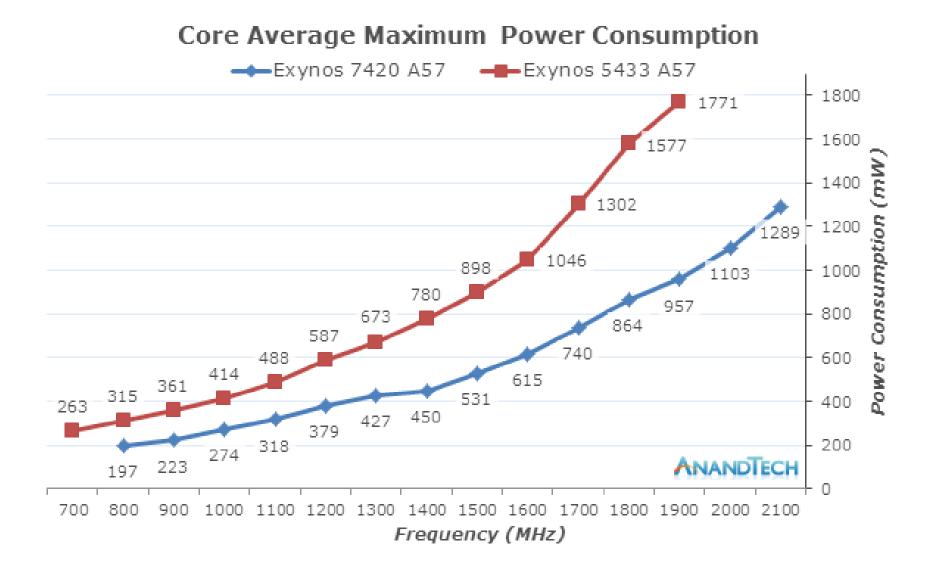

#### A57 power curves of the Exynos 7 7420 vs. the Exynos 5 5433 [16]

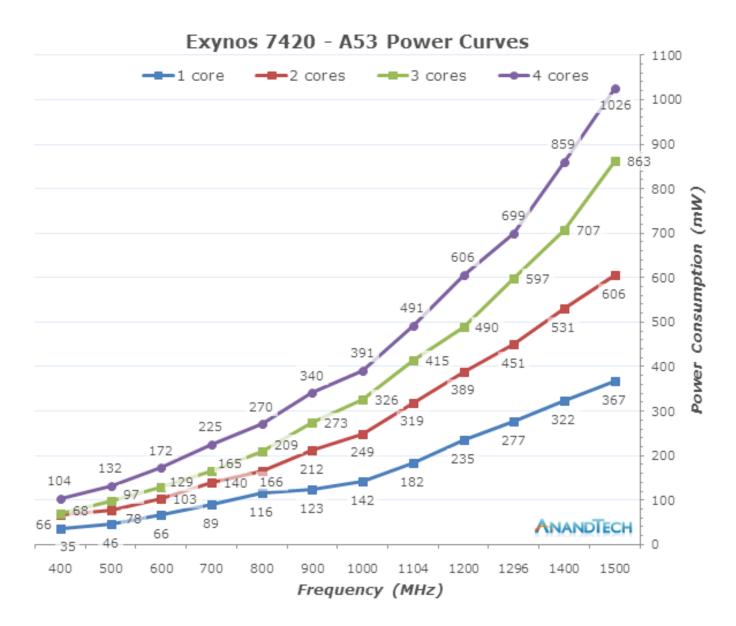

#### A53 power curves of the Exynos 7 7420 [16]

## Main innovations of the Samsung Exynos 7 7420

- a) Introducing binning in form of ASV groups

- b) Introducing AVS, called ASV (Adaptive Scaling Voltage) by Samsung

- c) Using LPDDR4 memory technology

- d) Implementing a hardware memory compressor

5.4.2 Introducing binning in form of ASV groups

# 5.4.2 Introducing binning in form of ASV groups

Before discussing Samsung's approach for binning let's recall traditional binning.

## Traditional binning of processors-1

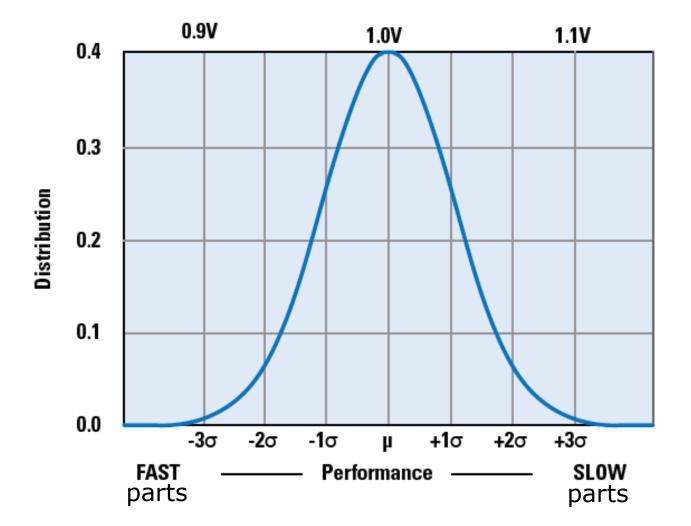

Electrical parameters of fabricated processor chips vary in a wide range, as illustrated for the distribution of minimum core voltages needed to sustain a given clock frequency, as measured post fabrication on the chips.

## 5.4.2 Introducing binning in form of ASV groups (3)

Example: Distribution of the minimum core voltage needed to sustain a given clock frequency measured on fabricated chips [17]

Example Supply V<sub>DD</sub> Variation

# Traditional binning of processors-2

- The distribution of electrical parameters on the fabricated chips will traditionally be addressed by the manufacturers by testing all chips at the factory and classifying them into a few number of groups, often called bins.

- These groups are considered then as different models of a processor line (termed also as SKUs (Stock Keeping Units)) with given sets of electrical parameters, first of all with different max. clock frequencies and will be sold typically at different sales prices.

- As an example, the next Table shows different models (SKUs) of a given processor line.

# Frequency bins of a given model (Intel's Core 2 Duo (2006))

| Product Name                  | <u>Intel Core2 Duo</u><br><u>E6400</u> | <u>Intel Core2 Duo</u><br><u>E6300</u> | <u>Intel Core2 Duo</u><br><u>E4300</u> |

|-------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|

| Code Name                     | <u>Conroe</u>                          | <u>Conroe</u>                          | <u>Conroe</u>                          |

| Essentials                    |                                        |                                        |                                        |

| Processor Number              | E6400                                  | E6300                                  | E4300                                  |

| Launch Date                   | Q3'06                                  | Q3'06                                  | Q3'06                                  |

| Lithography                   | 65 nm                                  | 65 nm                                  | 65 nm                                  |

| Recommended<br>Customer Price | \$128.00                               | N/A                                    | \$106.00                               |

| Performance<br># of Cores     | 2                                      | 2                                      | 2                                      |

| Base Frequency                | 2.13 GHz                               | 1.86 GHz                               | 1.80 GHz                               |

| Cache                         | 2 MB L2                                | 2 MB L2                                | 2 MB L2                                |

| Bus Speed                     | 1066 MHz FSB                           | 1066 MHz FSB                           | 800 MHz FSB                            |

| TDP                           | 65 W                                   | 65 W                                   | 65 W                                   |

| VID Voltage Range             | 0.8500V-1.5V                           | 0.8500V-1.5V                           | 0.8500V-1.5V                           |

## Samsung's approach to meet variations of electrical parameters of chips [16]

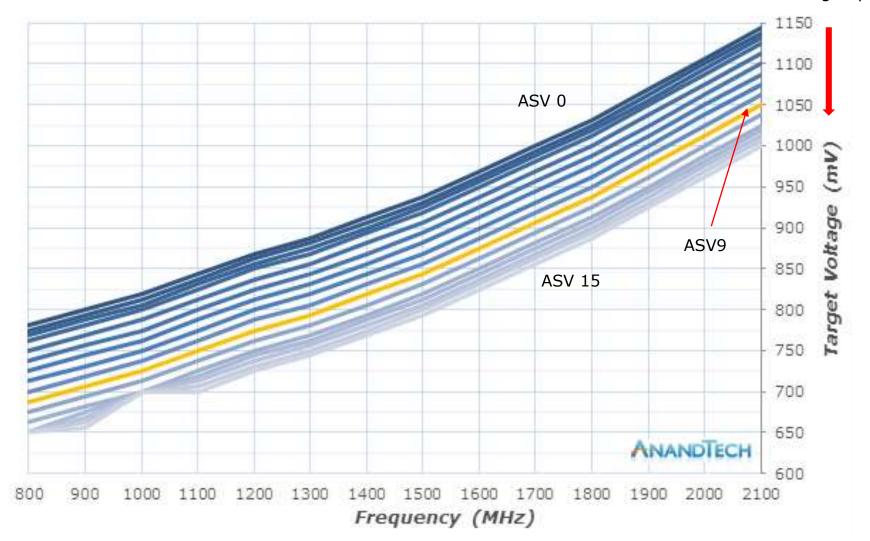

- In the traditional way of binning fabricated chips are classified according to their max. clock frequency into different groups and each group is sold as a different model of the same line, by contrast Samsung also tests their chips post manufacturing and assigns each chip to a group with similar characteristics, called an ASV group, but Samsung sells their chips of a given design only as a single model while marking each chip permanently with an ASV group identifier.

- For the Exynos Octa 7 7420 Samsung marks their chips with the ASV group identifiers ASV0 to ASV 15 by burning them into on-chip fuses.

A lower ASV value identifies a worse quality bin whereas a higher one a better quality bin.

Accordingly, ASV0 is the worst and ASV15 the best quality bin whereas bin 9 represents the median group.

• As an example, the next Figure shows the target voltage vs. core frequency characteristics of the ASV groups.

## 5.4.2 Introducing binning in form of ASV groups (7)

## Core voltage - core frequency curves of the Exynos 7 Octa 7420 [16]

Higher quality ASV group

5.4.3 Introducing AVS, called ASV (Adaptive Scaling Voltage) by Samsung

## 5.4.3 Introducing AVS called ASV (Adaptive Scaling Voltage) by Samsung (1)

5.4.3 Introducing AVS, called ASV (Adaptive Scaling Voltage) by Samsung

- Samsung's AVS technology is based on licensing National's PowerWise patent that is owned now by Texas Instrument (TI), as TI acquired National Semiconductor in 2011.

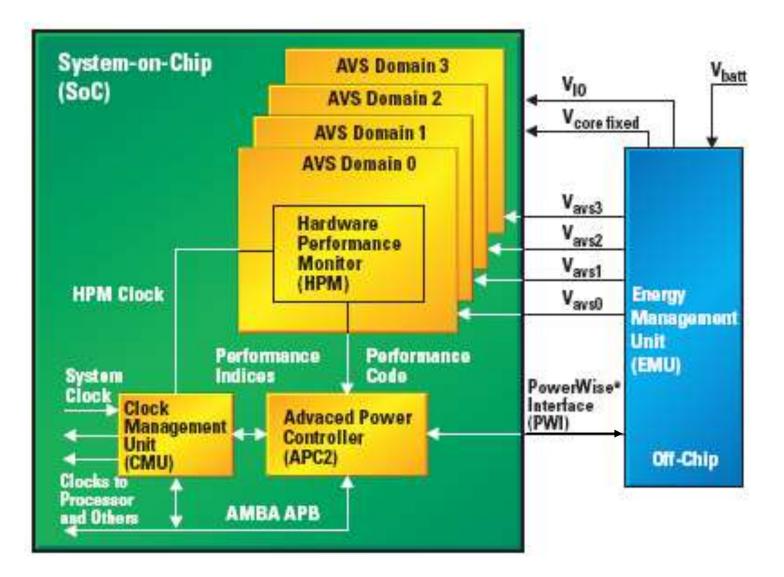

- Main components of National's PowerWise technology are seen in the next Figure.

## Main components of National's PowerWise technology [16]

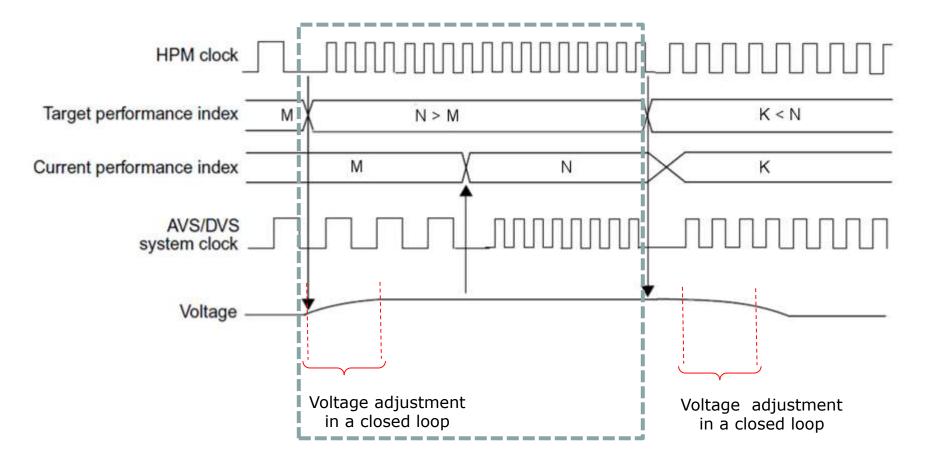

# Principle of operation of National's PowerWise technology (simplified)-1 [18]

- Based on the current activity of the considered core the OS forwards a Target performance index to the Clock Management Unit (CMU).

- The CMU forwards the Targer performance index to the Advanced Power Controller (APC) and also sets the clock frequency of the Hardware Performance Monitor (HPM) to the value corresponding to the Target performance index (this is needed for measuring the actual speed of the core).

- The next step is voltage adjustment in a closed loop.

- The HPM measures the propagation delay of the delay line (critical path) and sends a Performance code (PC) to the APC.

- The APC compares the received PC with the Reference Calibration Code (RCC) that is burnt to on chip fuses and directs the Energy Management Unit (EMU) via the PowerWise Interface (PWI) accordingly.

- If the PC indicates that the propagation delay is longer than required, APM will let the EMU to increase the core voltage (Vavs) to speed up the core and vice versa.

Nevertheless, depending on whether the gate delays on the chip are too long or too short there are two different avenues to follow subsequently.

#### Remark

The RCC is determined at the factory in a stress test, as the smallest Performance Code (PC) that allows a correct operation of the processor in the given frequency range, and it is burnt to on-chip fuses beyond the ASV identifier.

# Principle of operation of National's PowerWise technology (simplified)-2 [18]

- When the current performance needs to be increased by raising the current clock frequency, first the supply voltage will be increased adaptively in the closed loop and only subsequently, after the core voltage has already been adjusted will the clock rate be raised.

- To achieve this the APC informs the CMU about finishing the voltage adjustment and then the CMU will change the core clock to the desired value.

- By contrast, when a lower performance is requested than recently existing, the ASP immediately instructs the CMU to reduce the clock frequency to the requested value.

- In parallel the core voltage (Vavs) will be adjusted in the closed loop to the appropriate value.

5.4.3 Introducing AVS called ASV (Adaptive Scaling Voltage) by Samsung (5)

Changing P-states in National's PowerWise technology [18]

5.4.3 Introducing AVS called ASV (Adaptive Scaling Voltage) by Samsung (6)

#### Differences between Samsung's and National's AVS implementations

- aa) Implementing AVS in conjunction with ASV binning.

- ab) Use of an ARM M3 microcontroller as the APC unit that communicates with other units by mailbox messages.

### aa) Implementing AVS in conjunction with ASV binning

- Selecting the manufactured chips into up to 16 ASV groups has the benefit that the measured Reference Calibration Code (RCC) will fit with a much less tolerance to a particular chip than would in case when the manufactured chips would be selected into a much less number of models.

- This has a further benefit since then the voltage adjusting process becomes shorter.

5.4.3 Introducing AVS called ASV (Adaptive Scaling Voltage) by Samsung (8)

ab) Use of an ARM M3 microcontroller as the APC unit that communicates with other units by mailbox messages [16]

- Instead of making use of the Advanced Power Controller (APC) unit offered by National as part of the PowerWise technology Samsung implements the APC in form of an ARM M3 microcontroller.

- The M3 communicates with the other system components by mailbox messages.

Mailboxes represent a kind of interprocess communication that is used typically between different architectures such that each unit can only write messages to its own mailbox (being in the RAM space) but is able to read all other mailboxes. Reducing core voltage and power consumption by using AVS in the Exynos 7 7420 vs. the 5 5433 for different clock rates and ASV groups [19] (Note: Data are not corresponding to the previous figure).

|                       | Exynos 5433 | Exynos 7420 | Differenz  |

|-----------------------|-------------|-------------|------------|

| A57 1,9 GHz bei ASV9  | 1200,00 mV  | 975,00 mV   | -225,00 mV |

| A57 1,9 GHz bei ASV15 | 1125,00 mV  | 912,50 mV   | -212,50 mV |

| 457 800 MHz bei ASV9  | 900,00 mV   | 687,50 mV   | -224,50 mV |

| A57 800 MHz bei ASV15 | 900,00 mV   | 625,00 mV   | -275,00 mV |

| A53 1,3 GHz bei ASV9  | 1112,50 mV  | 950,00 mV   | -162,50 mV |

| A53 1,3 GHz bei ASV15 | 1062,50 mV  | 900,00 mV   | -162,50 mV |

| A53 400 MHz bei ASV9  | 787,50 mV   | 656,25 mV   | -131,25 mV |

| A53 400 MHz bei ASV15 | 750,00 mV   | 606,25 mV   | -143,75 mV |

| GPU 700 MHz bei ASV9  | 1050,00 mV  | 800,00 mV   | -250,00 mV |

| GPU 700 MHz bei ASV15 | 1012,50 mV  | 750,00 mV   | -262,50 mV |

| GPU 266 MHz bei ASV9  | 800,00 mV   | 668,75 mV   | -131,25 mV |

| GPU 266 MHz bei ASV15 | 762,50 mV   | 606,25 mV   | -156,25 mV |

5.4.4 Introducing LPDDR4

## 5.4.4 Introducing LPDDR4

Using LPDDR4 almost doubles the memory transfer rate of the 32-bit dual channel memory compared to the LPDDR3's implemented in the Exynos 7 5433 model, actually from 1650 MT/s to 3104 MT/s.

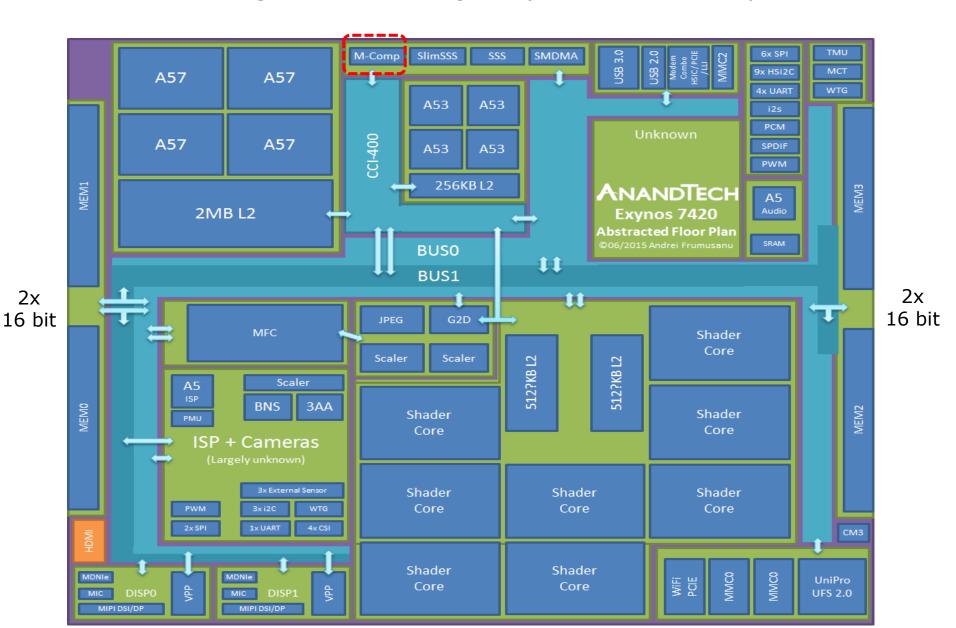

5.4.5 Implementing a hardware memory compressor

### 5.4.5 Implementing a hardware memory compressor [16]

- This is a hardware unit, called M-Comp on the block diagram of the processor that is designed especially for Android.

- We note that beginning with the Android 4.4 kernel DRAM compression has already become a validated part of the OS and all devices support this feature.

- Most vendors support it by the "zram" mechanism, which is a ramdisk with compression support.

The kernel makes use of it as a swapping device to store rarely used memory pages.

Also Samsung had implemented this compression mechanism in their Galaxy devices as far back as Android 4.1.

- The Galaxy S6 implements a more advanced compressor scheme called "zswap" which is able to compress memory pages before they need to get swapped out to a swap device, so it's a more optimized mechanism that sits closer to the kernel's memory management part.

- As an example "zswap" may compress 1.21GB of pages into 341MB of physical memory.

This is however yet a software implementation running on the CPU cores.

• The available dedicated hardware compressor (M-Comp) is currently not yet activated and its use needs OS support to be provided in a future OS update.

5.5: Samsung's first SoC including an in-house designed CPU core (the M1): the Exynos 8 Octa 8890 (2016)

- 5.5.1 The Exynos 8 Octa 8890 Overview

- 5.5.2 The M1 (Mongoose) core

## 5.5.1 The Exynos 8 Octa 8890 - Overview

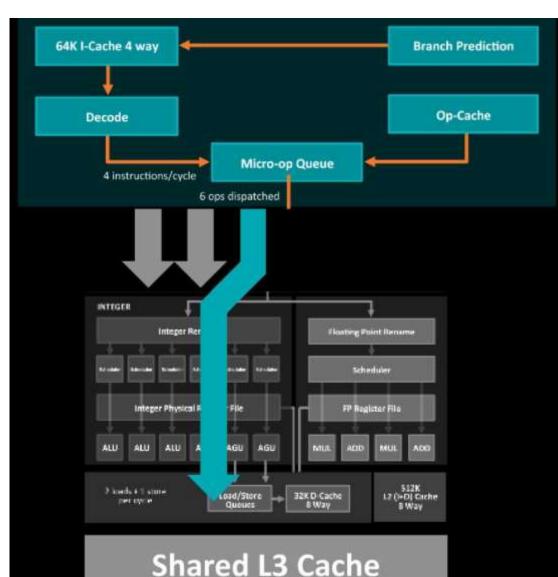

#### 5.5.1 The Exynos 8 Octa 8890 - Overview

- It is fabricated based on Samsung's 2. gen. 14 nm (Low-Power Plus (LPP) FinFET process.

- It is the kernel piece of Samsung's Galaxy S7, S7 Edge and Galaxy Note 7.

- Introduced in Q1/2016.

### Main features of Samsung's Exynos 8 Octa 8890 (2016)

| SoC                              |                 | CPU           |                           |             |                    |                                                     | Memory                                           | Availab       | Utilizing devices                                                                                                   |  |

|----------------------------------|-----------------|---------------|---------------------------|-------------|--------------------|-----------------------------------------------------|--------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------|--|

| Model number                     | fab             | Instr.<br>set | Cores                     | No of cores | fc<br>(GHz)        | GPU                                                 | technology                                       | ility         | (examples)                                                                                                          |  |

| Exynos 5 Octa<br>(Exynos 5420)   | 28 nm<br>HKMG   |               | Cortex-A15+<br>Cortex-A7  | 4+4         | 1.8-1.9<br>1.2-1.3 | ARM Mali-T628 MP6<br>@ 533 MHz;<br>109 GFLOPS       | 32-bit DCh LPDDR3e-<br>1866 (14.9 GB/sec)        | Q3<br>2013    | Samsung Chromebook 2<br>11.6", Samsung Galaxy Note<br>3/Note 10.1/Note Pro 12.2,<br>Samsung Galaxy Tab Pro/Tab<br>S |  |

| Exynos 5 Octa<br>(Exynos 5422)   | 28 nm<br>HKMG   | ARM<br>v7     | Cortex-A15+<br>Cortex-A7  | 4+4         | 1.9-2.1<br>1.3-1.5 | ARM Mali-T628 MP6<br>@ 533 MHz 109<br>GFOPS         | 32-bit DCh<br>LPDDR3/DDR3-1866<br>(14.9 GB/sec)  | Q2<br>2014    | Samsung Galaxy S5<br>(SM-G900H)                                                                                     |  |

| Exynos 5 Octa<br>(Exynos 5800)   | 28 nm<br>HKMG   |               | Cortex-A15+<br>Cortex-A7  | 4+4         | 2.1<br>1.3         | ARM Mali-T628 MP6<br>@ 533 MHz<br>109 GFLOPS        | 32-bit DCh<br>LPDDR3/DDR3-1866<br>(14.9 GB/sec)  | Q2<br>2014    | Samsung Chromebook 2<br>13,3"                                                                                       |  |

| Exynos 5 Octa<br>(Exynos 5430)   | 20 nm<br>HKMG   |               | Cortex-A15+<br>Cortex-A7  | 4+4         | 1.8-2.0<br>1.3-1.5 | ARM Mali-T628 MP6<br>@ 600 MHz;<br>122 GFLOPS       | 32-bit DCh<br>LPDDR3e/DDR3-2132<br>(17.0 GB/sec) | Q3<br>2014    | Samsung Galaxy Alpha (SM-<br>G850F)                                                                                 |  |

| Exynos 7 Octa<br>(Exynos 5433    | 20 nm<br>HKMG   |               | Cortex-A57+<br>Cortex-A53 | 4+4         | 1.9<br>1.3         | Mali-T760 MP6 @<br>700 MHz; 206<br>GFLOPS (FP16)    | 32-bits DCh LPDDR3-<br>1650 (13.2 GB/s)          | Q3/Q4<br>2014 | Samsung Galaxy Note 4 (SM-<br>N910C)                                                                                |  |

| Exynos 7 Octa<br>(Exynos 7420)   | 14 nm<br>FinFET |               | Cortex-A57+<br>Cortex-A53 | 4+4         | 2.1<br>1.5         | Mali-T760 MP8 @<br>772 MHz; 227<br>GFLOPS (FP16)    | 32-bits DCh LPDDR4-<br>3104 (24.9 GB/s)          | Q2<br>2015    | Samsung Galaxy S6<br>S6 Edge                                                                                        |  |

| Exynos 7 Octa<br>(Exynos 7885)   | 14 nm<br>HKMG   | ARM           | Cortex-A73+<br>Cortex-A53 | 4+4         | 2.2<br>1.6         | Mali-G71 MP2                                        | 32-bits DCh LPDDR4x                              | Q1<br>2016    | Samsung Galaxy A8                                                                                                   |  |

| Exynos 8 Octa<br>(Exynos 8890)   | 14 nm<br>FinFET |               | Samsung M1+<br>Cortex-A53 | 4+4         | 2.6-2.3<br>1.6     | Mali-T880 MP12 @<br>650 MHz; 265.2<br>GFLOPS (FP16) | 32-bits DCh LPDDR4-<br>3588 (28.7 GB/s)          | Q1<br>2016    | Samsung Galaxy S7<br>Samsung Galaxy S7 Edge                                                                         |  |

| Exynos 9 Series<br>(Exynos 8895) | 10 nm<br>FinFET |               | Samsung M2+<br>Cortex-A53 | 4+4         | 2.5<br>1.7         | Mali-G71 MP20                                       | 32-bits DCh?<br>LPDDR4x                          | Q2<br>2017    | Samsung Galaxy S8<br>Samsung Galaxy S8 Plus                                                                         |  |

| Exynos 9 Series<br>(Exynos 9810) | 10 nm<br>FinFET |               | Samsung M3+<br>Cortex-A55 | 4+4         | 2.9<br>1.9         | Mali-G72 MP18                                       | 32-bits DCh?<br>LPDDR4x                          | Q1<br>2018    | Samsung Galaxy S9<br>Samsung Galaxy S9 Plus                                                                         |  |

## Main innovations of the Exynos 8 Octa 8890 processor

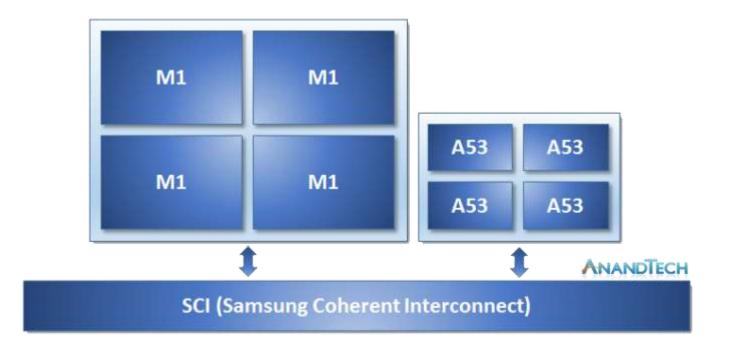

- It is built up as a big.LITTLE architecture while as big cores Samsung makes use of their first in-house core design, designated as the M1 (Mongoose) core.

- It is based on Samsung's custom SCI (Samsung Coherent Interconnect) bus.

- It is Samsung's first application processor with an integrated modem.

Figure: Basic structure of Samsung's Eynos 8 Octa 8890 [20]

## Contrasting key features of high-end 14/16 nm mobile processors [21]

| High-End SoCs Specifications |                                                    |                                                            |                                                                            |                                                    |  |

|------------------------------|----------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------|--|

| SoC                          | Qualcomm<br>Snapdragon 820                         | Huawei<br>Kirin 950                                        | Samsung<br>Exynos 8 Octa 8890                                              | Samsung<br>Exynos 7 Octa 7420                      |  |

| CPU                          | 2x Kryo@1.593GHz                                   | 4x Cortex A72 @2.3 Ghz                                     | 4x A53@1.586GHz                                                            | 4x A53@1.50GHz                                     |  |

|                              | 2x Kryo@2.150GHz                                   | 4x Cortex A53 @1.8Ghz                                      | 4x Exynos M1 @<br>2.60GHz<br>(1-2 core load)<br>2.29GHz<br>(3-4 core load) | 4x A57@2.1GHz                                      |  |

| Memory<br>Controller         | 2x 32-bit<br>LPDDR4 @<br>1803 MT/s<br>28.8GB/s b/w | 2x 32-bit<br>LPDDR3 or LPDDR4 @<br>1333 MT/s<br>21.32 GB/s | 2x 32-bit<br>LPDDR4 @<br>1794 MT/s<br>28.7GB/s b/w                         | 2x 32-bit<br>LPDDR4 @<br>1555 MT/s<br>24.8GB/s b/w |  |

| GPU                          | Adreno 530<br>@ 624 MHz                            | ARM Mali T860<br>,@ 900 MHz                                | Mali T880MP12<br>@ 650 MHz                                                 | Mali T770MP8<br>@ 770 MHz                          |  |

| Mfc.<br>Process              | Samsung<br>14nm LPP                                | TSMC<br>16 nm FinFET+                                      | Samsung<br>14nm LPP                                                        | Samsung<br>14nm LPE                                |  |

5.5.2 The M1 (Mongoose) core

### 5.5.2 The M1 (Mongoose) core (1)

## 5.5.2 The M1 (Mongoose) core

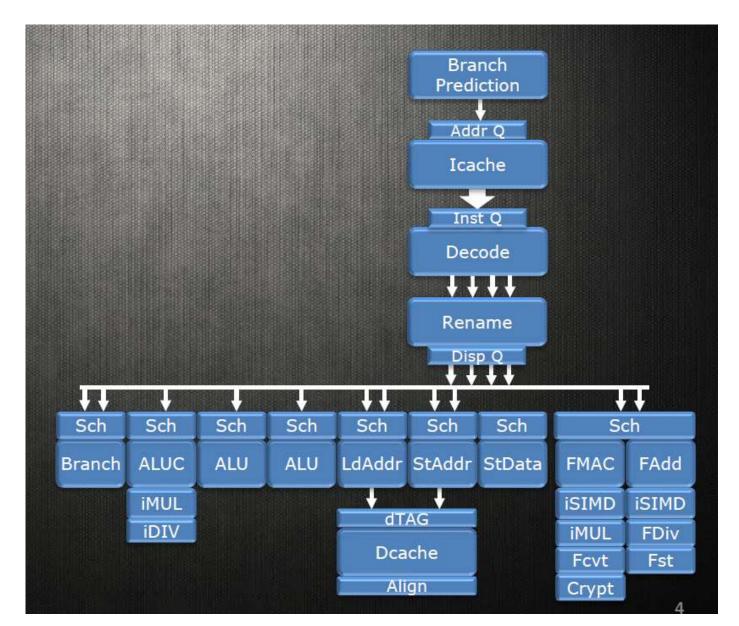

## Main features of the M1 (Mongoose) core

- It implements the ARMv8 ISA.

- It has a 4-wide front-end.

- It has neural net (perceptron) based branch prediction.

- The core is an out-of-order 2.6 GHz design.

- The core design lasted 3 years.

- Subsequently, we point out main features of the Mongoose core design.

5.5.2 The M1 (Mongoose) core (2)

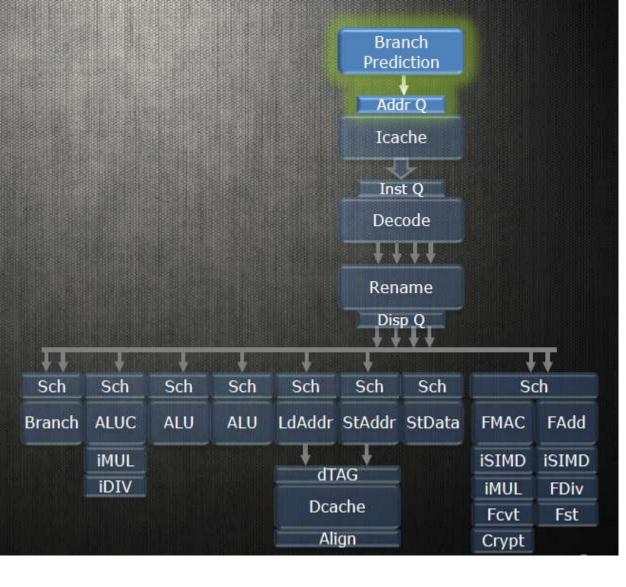

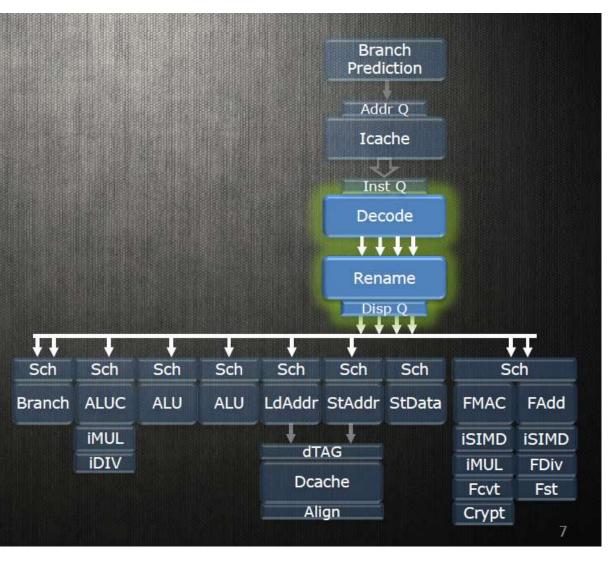

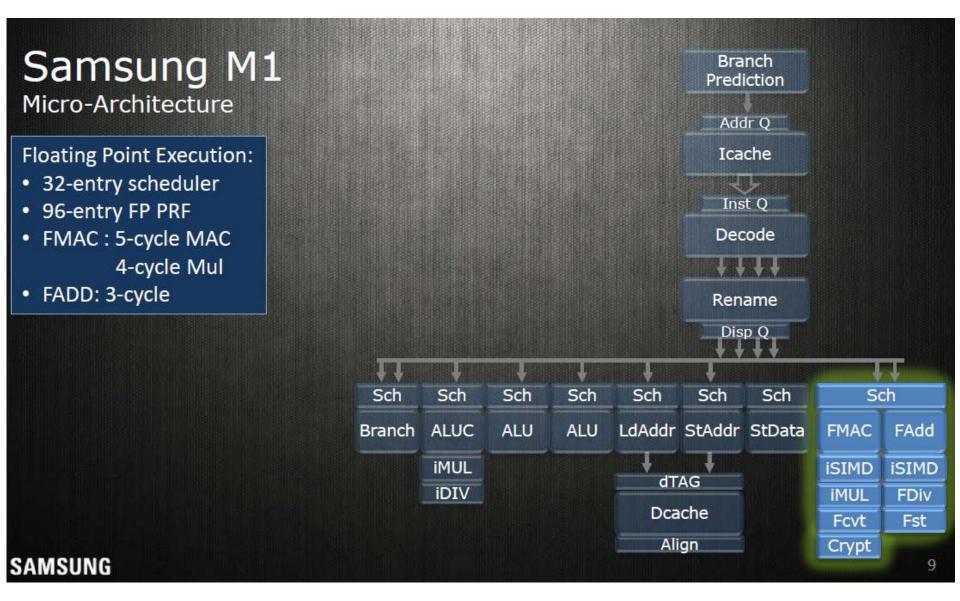

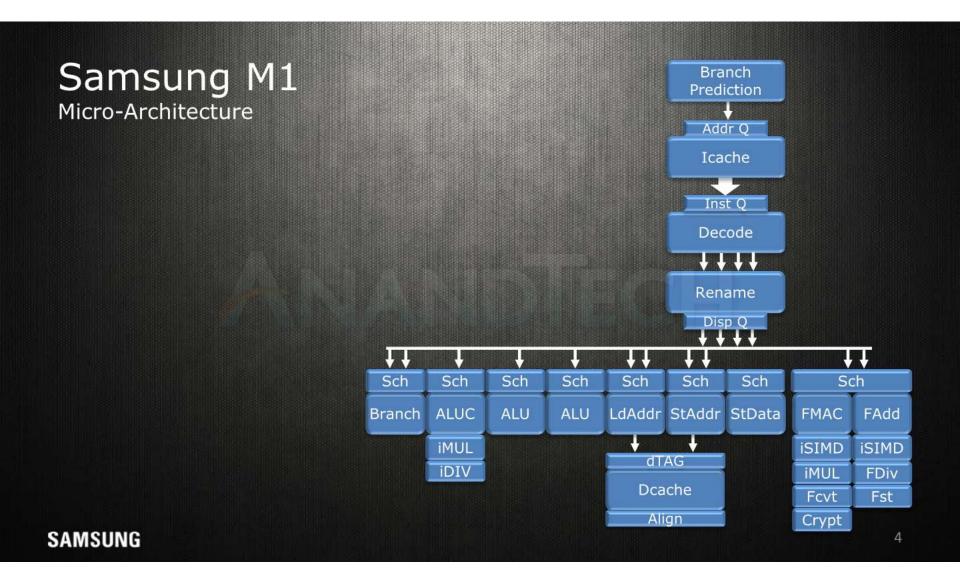

#### The overall microarchitecture of the M1 core [22]

### 5.5.2 The M1 (Mongoose) core (3)

## Neural net based branch prediction [22]

# Samsung M1 Micro-Architecture

#### **Branch Prediction:**

- Neural Net based predictor

- Two branches/cycle

- Fetch up to 24-bytes/cycle

- 64-entry microBTB

- 4k-entry mainBTB

- 64-entry Call/Return Stack

- Indirect Predictor

- Loop Predictor

- Decoupled AddrQ

Remarks on the use of perceptrons for branch prediction

- Each miss prediction causes a number of wasted cycles in instruction processing, the more the longer the instruction pipeline is.

- The efficiency of branch prediction and prefetching are decisive for the achievable ILP and thus for the processor performance.

- Accordingly, the evolution of processors was accompanied by by the evolution of branch prediction.

- Recent branch predictors consists of a number of dedicated predictors addressing different types of branches, like direct or indirect branches, loops etc.

- Perceptron based (called also neural) branch prediction was first suggested by Vintan (U. Sibiu) [23] in 1999 and then by Jimenez and Lin (U. Texas) [24] in (2001).

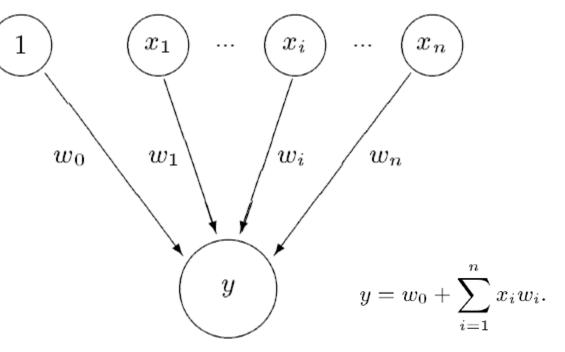

The perceptron model: a single layer perceptron [24]

- The perceptron, introduced in 1962, is in fact an artificial neuron.

- It receives a number of inputs (xi) that are bipolar (-1 or 1) and calculates an output value (y) that is the sum of the product of the input values (xi) and given weights (wi), as shown below.

- A perceptron can be trained to provide a prediction.

Figure: A single layer perceptron [24]

#### 5.5.2 The M1 (Mongoose) core (6)

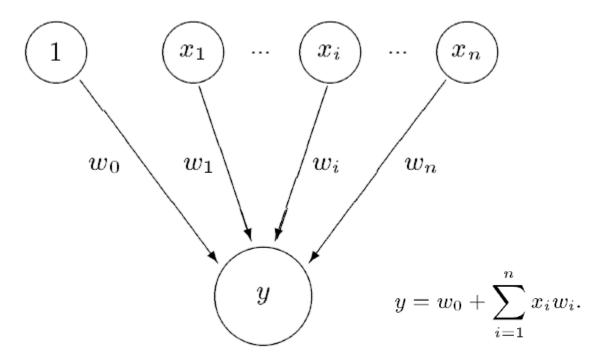

Principle of using perceptrons for branch prediction [24]

- Inputs (xi) are taken from branch history and are -1 or +1.

- The weights (wi) are small integer values that are learned by on-line training,

- Training finds correlation between history and outcome.

- The output (y) is the dot product of xi's and wi's, as shown below.

- The output (y) is interpreted as prediction is taken if  $y \ge 0$ .

- Once the outcome of the prediction (y) becomes known the training algorithm uses this value to update the weights (wi).

Figure: A single layer perceptron [24]

### 5.5.2 The M1 (Mongoose) core (7)

Published use of perceptrons (neural networks) for branch prediction

- AMD Bobcat (2011)

Jaguar (2013)

Piledriver (2012)

Zen (2017)

- Oracle SPARCT4 (2011)

- Samsung Exynos Octa 8 8890 M1 (Mongoose) core 2016

Implementation of perceptron based (neural) branch prediction [24]

- Actually there are no published details about the perceptron based (neural) branch predictors used in the processors enlisted above.

- As an example below we show AMD's related slide "revealing the use of neural branch prediction in their Zen processor (2017).

### 5.5.2 The M1 (Mongoose) core (9)

## Example: Perceptron based branch prediction in AMD's Zen microarch. [58]

### **Scary Smart Prediction**

- A true artificial network inside every "Zen" processor

- Builds a model of the decisions driven by software code execution

- Anticipates future decisions, pre-load instructions, choose the best path through the CPU

### Achieved accuracy of recent sophisticated branch predictors

- Since 2004 the The Journal of Instruction-Level Parallelism organizes each third year a Championship Branch Prediction (CBP-1 to CPB5) [25].

- Presented predictors for conditional branches are evaluated on a given trace set by calculating the weighted average of Mispredictions Per Thousand Instructions (MPTI).

- Predictors must be implemented within a fixed storage budget of 8 kB, 64 kB or unlimited.

- The best results reveal astonishingly low misprediction rates [26]:

| Storage budget | MPTI |

|----------------|------|

| 8 KB           | 5.3  |

| 64 KB          | 4.1  |

| Unlimited      | 3.0  |

#### Remarks on Samsung's perceptron based branch predictor implementation in Zen

- The designer of AMD's first branch prediction logic for the first microprocessor with a neural network branch predictor (AMD Bobcat) (James Dundas) left AMD and joined Samsung in 2012 [27].

- Also the Chief Architect of the Bobcat processor (Brad Burgess) left AMD, joined Samsung and became the Chief CPU Architect in 2011 [28].

### 5.5.2 The M1 (Mongoose) core (12)

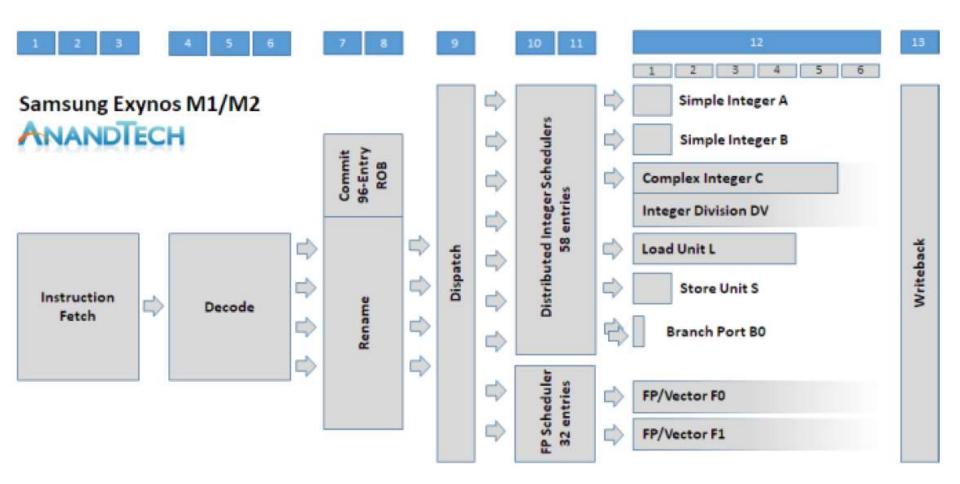

## 4-wide front end rather than 2 to 3 as in most mobiles [22]

# Samsung M1 Micro-Architecture

#### Decode / Rename / Retire:

- Decode 4 inst/cycle

- AArch64, AArch32

- Sequencer for multi-uop

- Rename 4-uops/cycle

- Special renaming for FP

- Fast map recovery

- Retire 4-uops/cycle

- 96-entry ROB

- Dispatch 4-uops/cycle

#### SAMSUNG

#### 5.5.2 The M1 (Mongoose) core (12b)

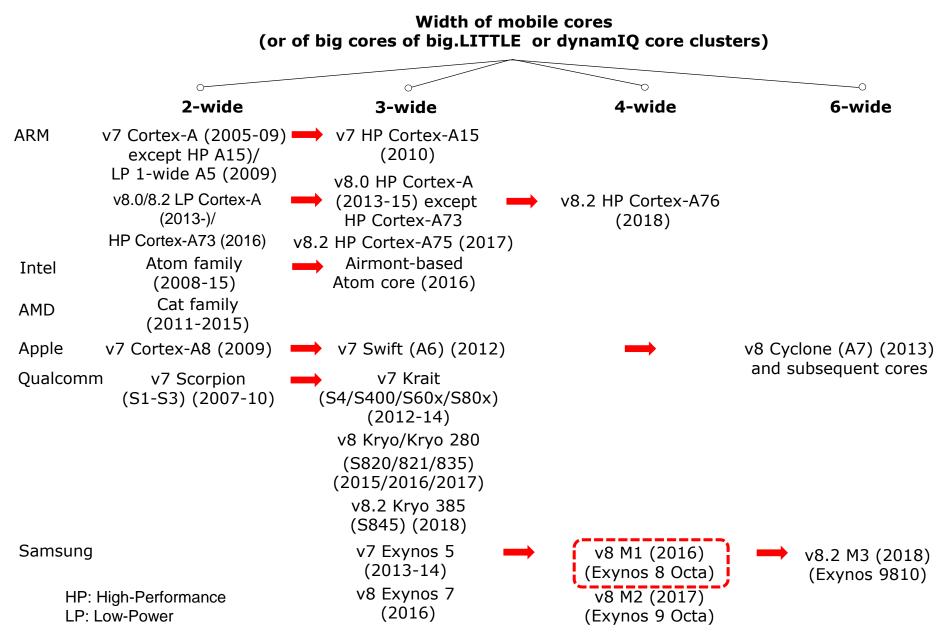

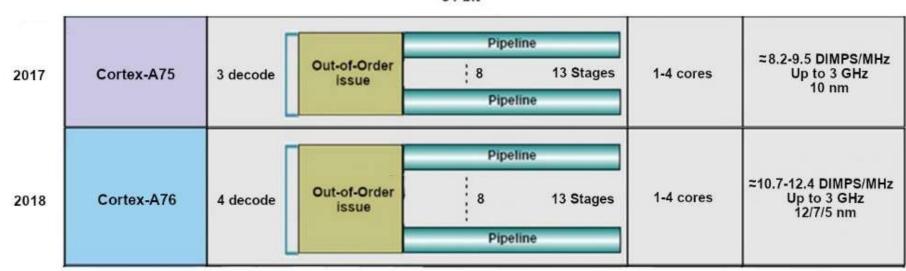

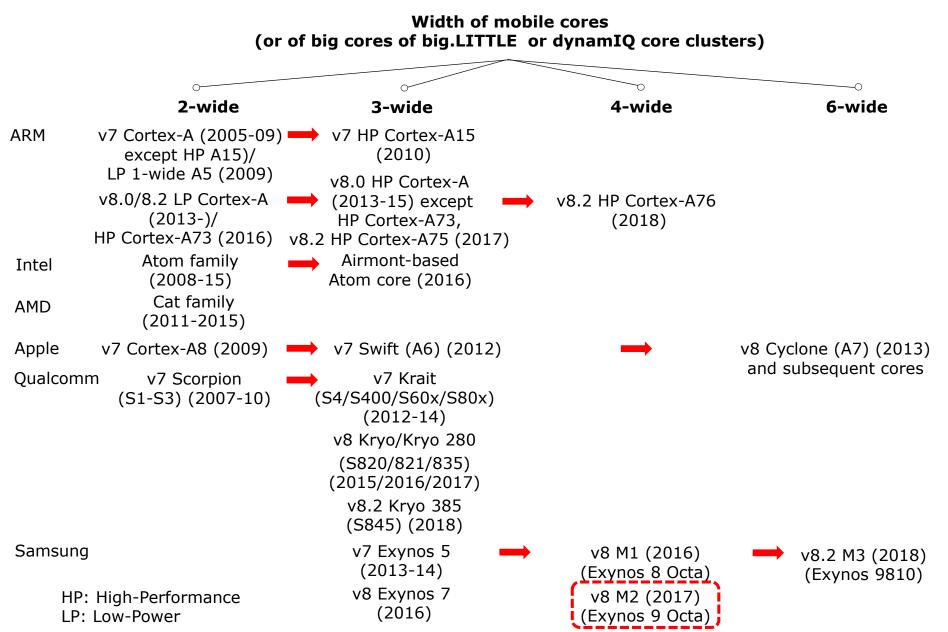

#### Evolution of the width of mobile cores

## 5.5.2 The M1 (Mongoose) core (13)

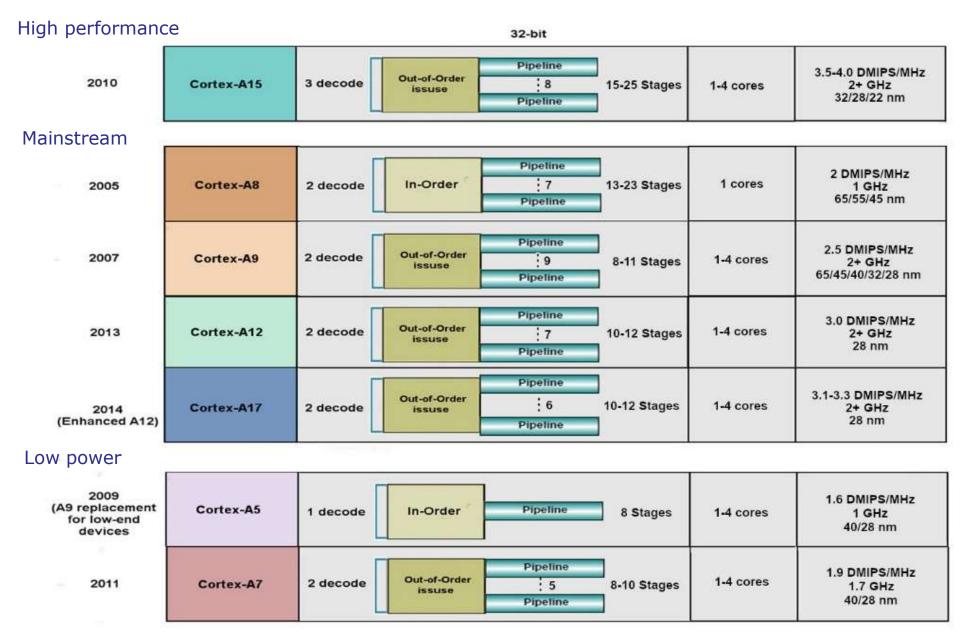

### By contrast: Width of ARM v7 ISA based microarchitectures (based on [29])

### 5.5.2 The M1 (Mongoose) core (14)

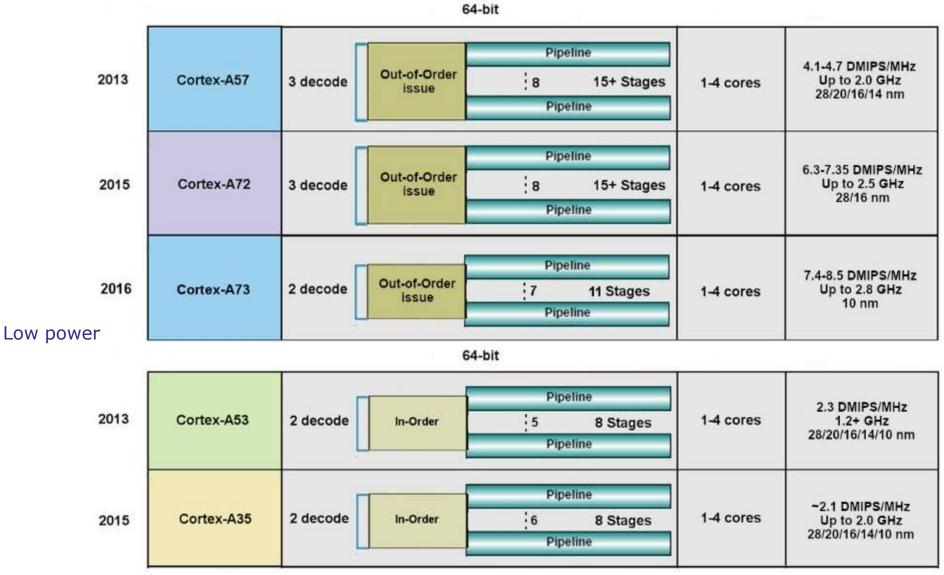

### By contrast: Width of ARM v8.0 ISA based microarchitectures (based on [29])

#### High performance

### 5.5.2 The M1 (Mongoose) core (14b)

By contrast: Width of ARM v8.2 ISA based microarchitectures (based on [29])

#### High performance

64-bit

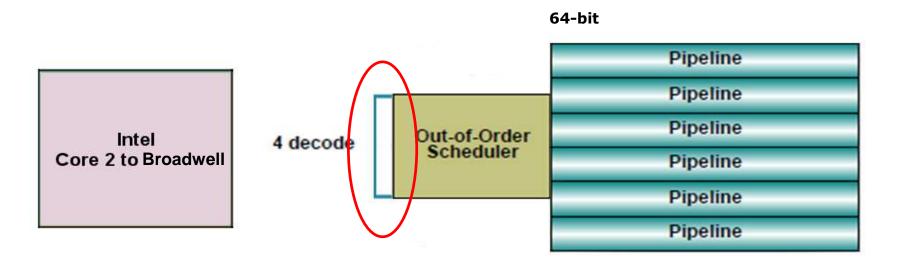

By contrast: Front-end width of Intel's and AMD's recent microarchitectures

#### Remarks

- Intel introduced 4-wide front ends beginning with their Core 2 (2006).

- Since Skylake Intel widened the front-end of its processor to 5.

- AMD introduced 4-wide microarchitectures only five years later, along with the Bulldozer line in 2011.

### 5.5.2 The M1 (Mongoose) core (16)

## 7-wide FX- and Load/Store scheduler [22]

# Samsung M1 Micro-Architecture

#### Integer Execution:

- Issue up to 7 uops/cycle

- 96-entry integer PRF

- 58-entry distributed sched.

- Branch resolution

- ALUC three source uops

- ALU two source uops

- Load Address Adder

- Store Address Adder

- Store Data

SAMSUNG

5.5.2 The M1 (Mongoose) core (17)

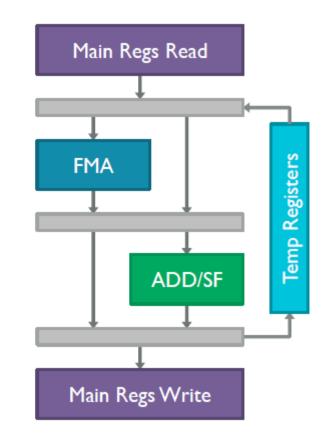

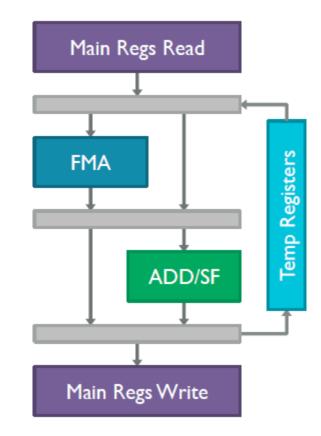

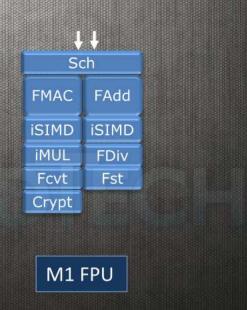

## 2-wide FP-issue, FMAC and FADD operations [22]

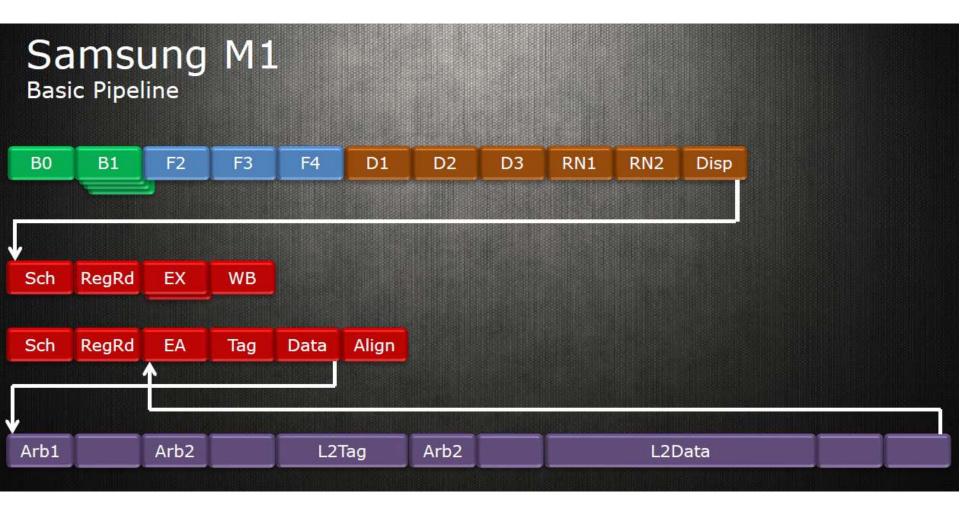

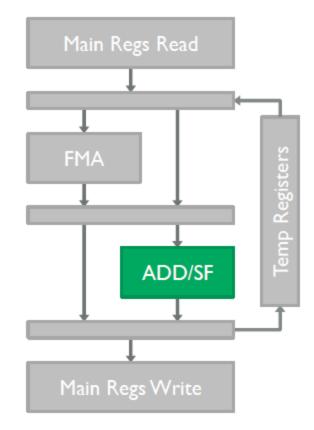

Pipeline structure of the M1 [22]

### 5.5.2 The M1 (Mongoose) core (19)

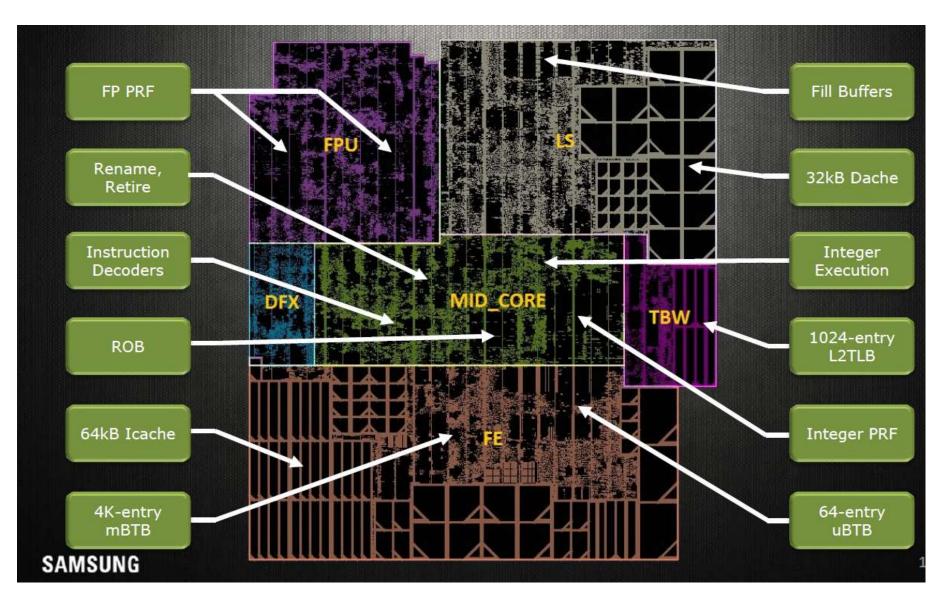

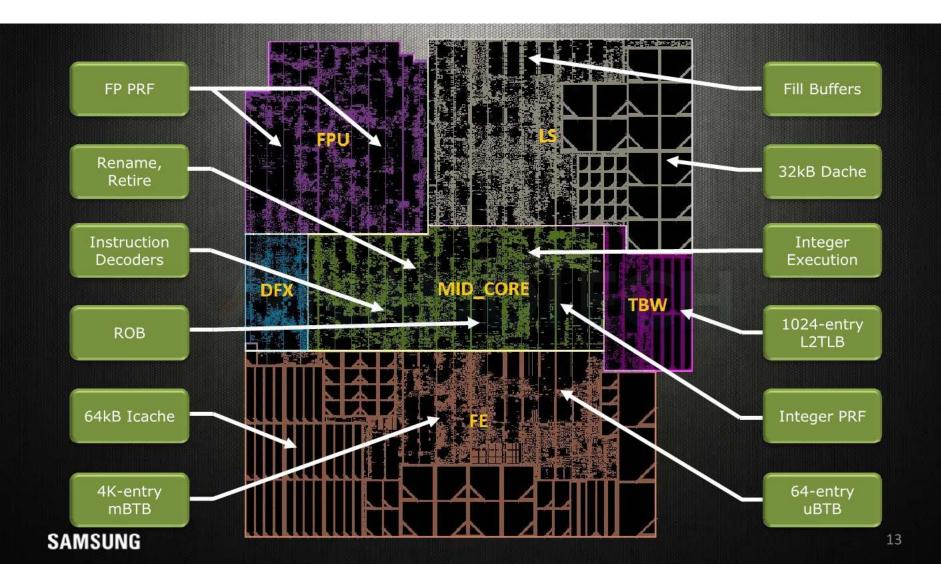

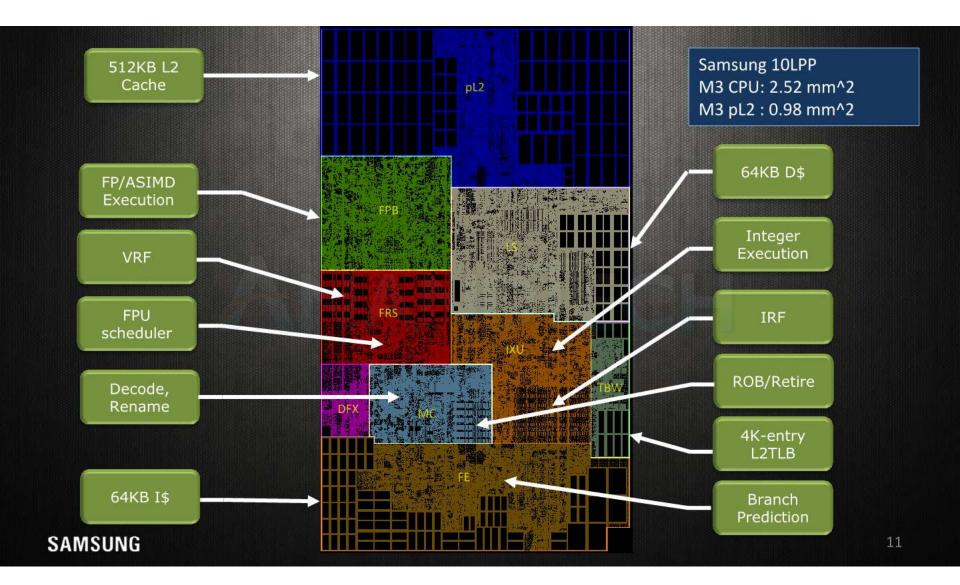

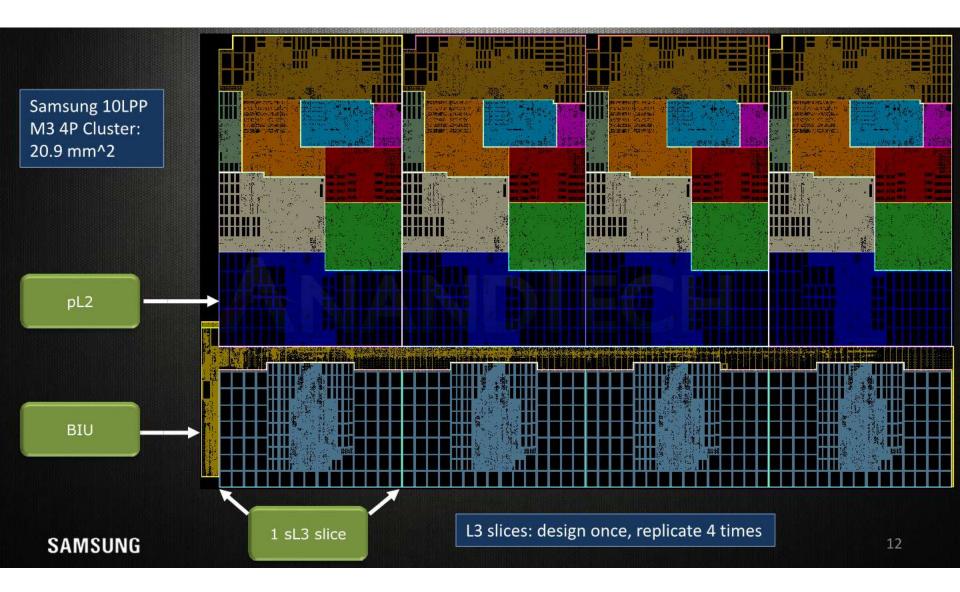

#### Die layout of the M1 core [22]

#### 5.5.2 The M1 (Mongoose) core (20)

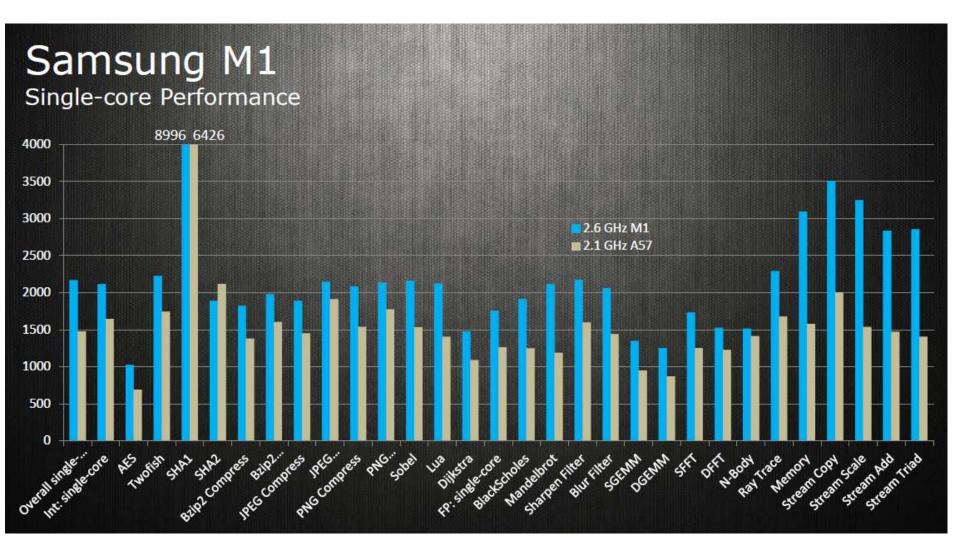

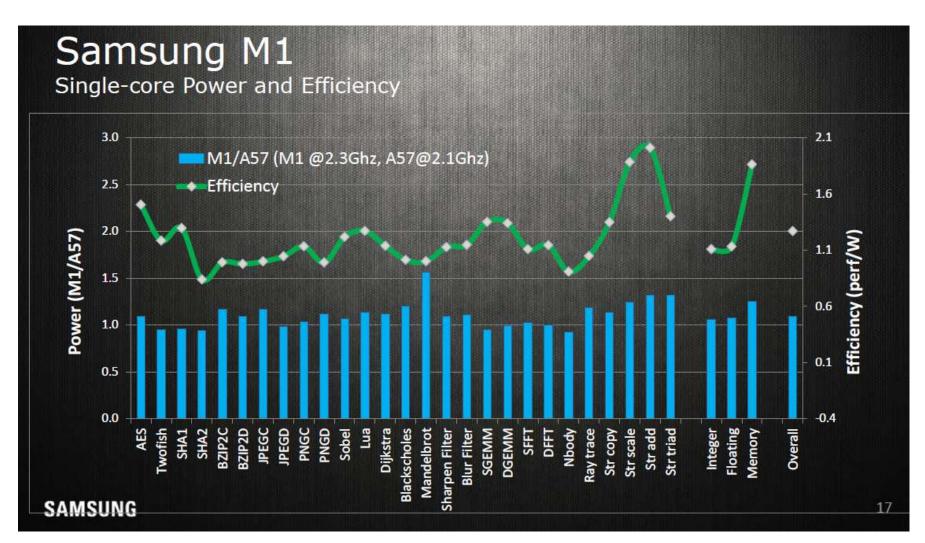

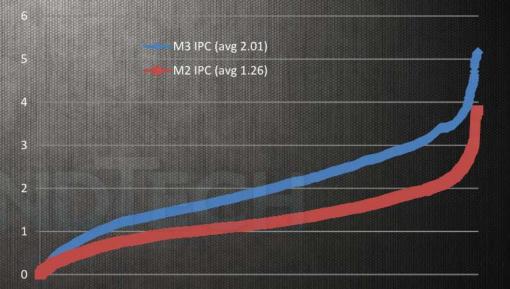

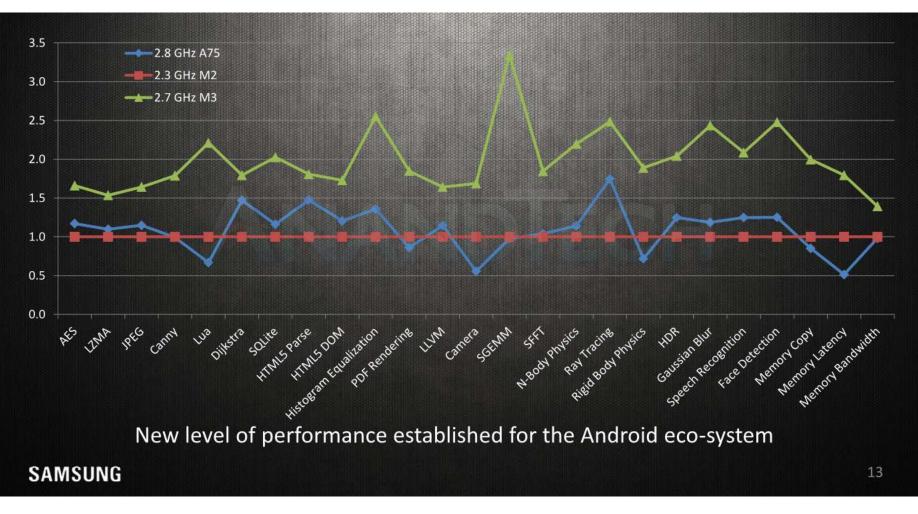

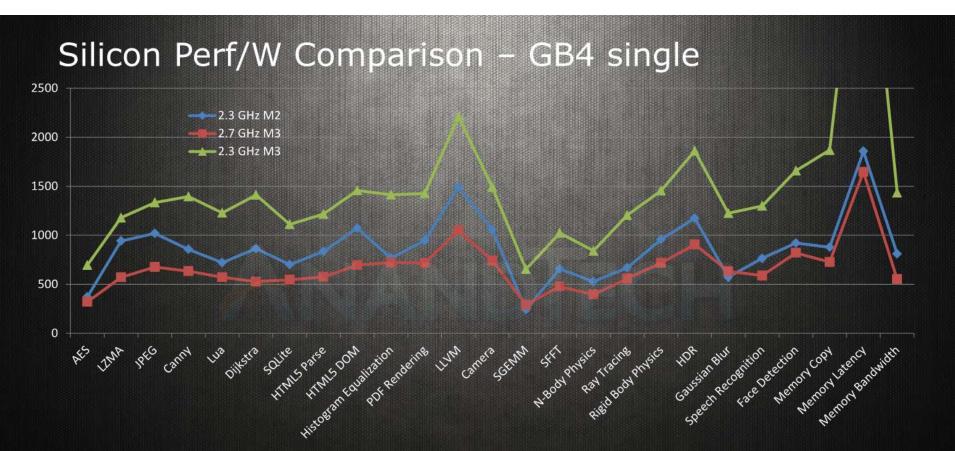

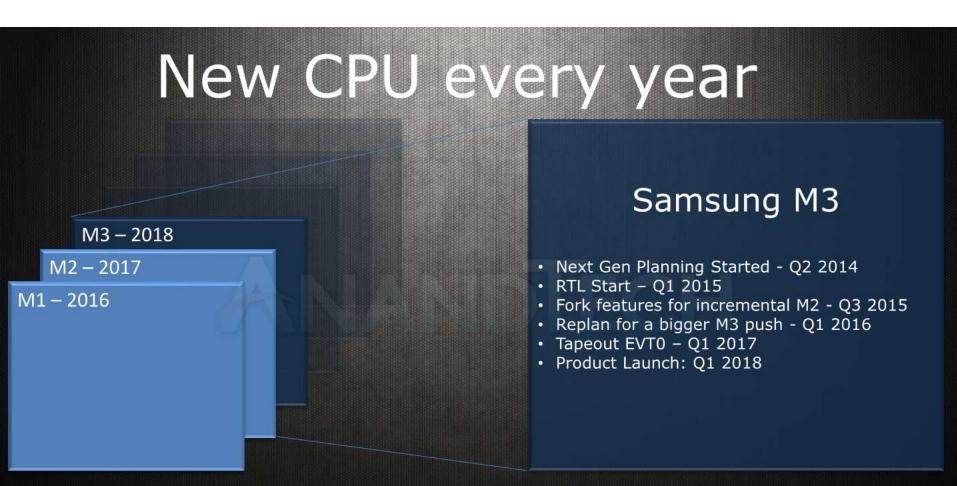

Single-core performance of the 2.6 GHz M1 vs. the 2.1 GHz A57 [22]

#### 5.5.2 The M1 (Mongoose) core (21)

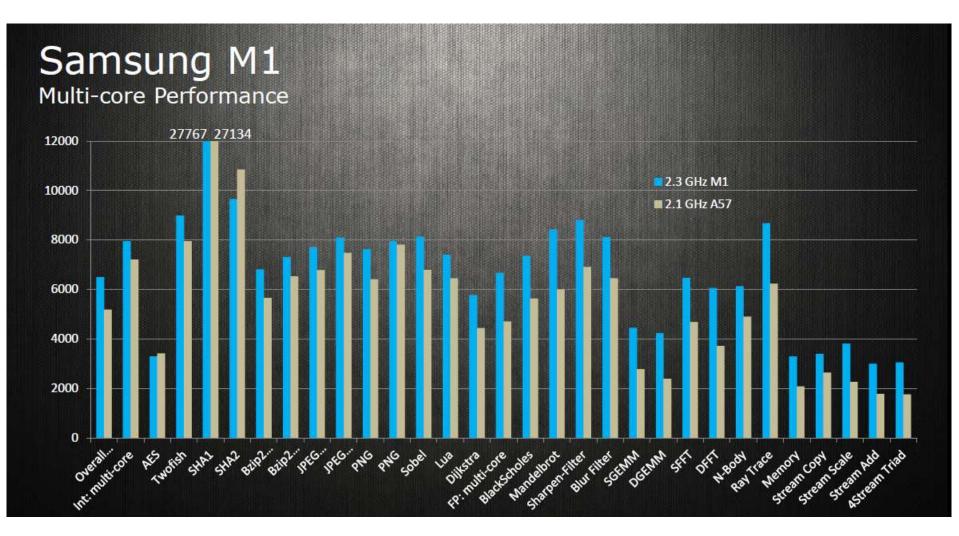

Multi-core performance of the 2.3 GHz M1 vs. the 2.1 GHz A57 [22]

5.5.2 The M1 (Mongoose) core (22)

Single core power and efficiency data of the M1 vs. the A57 [22]

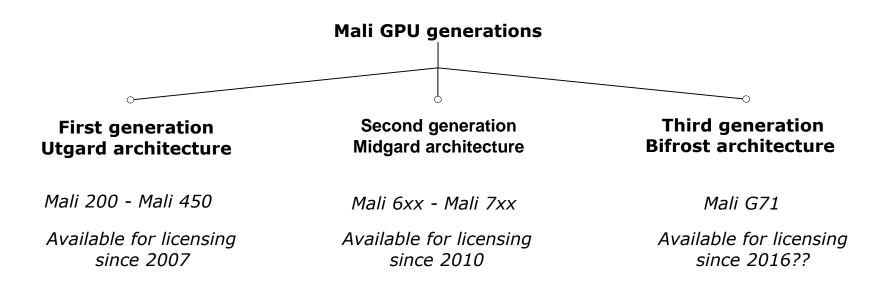

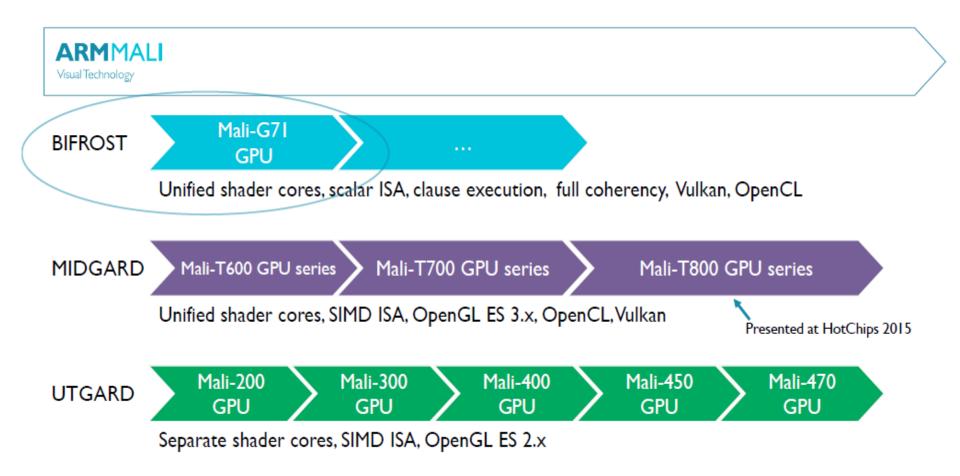

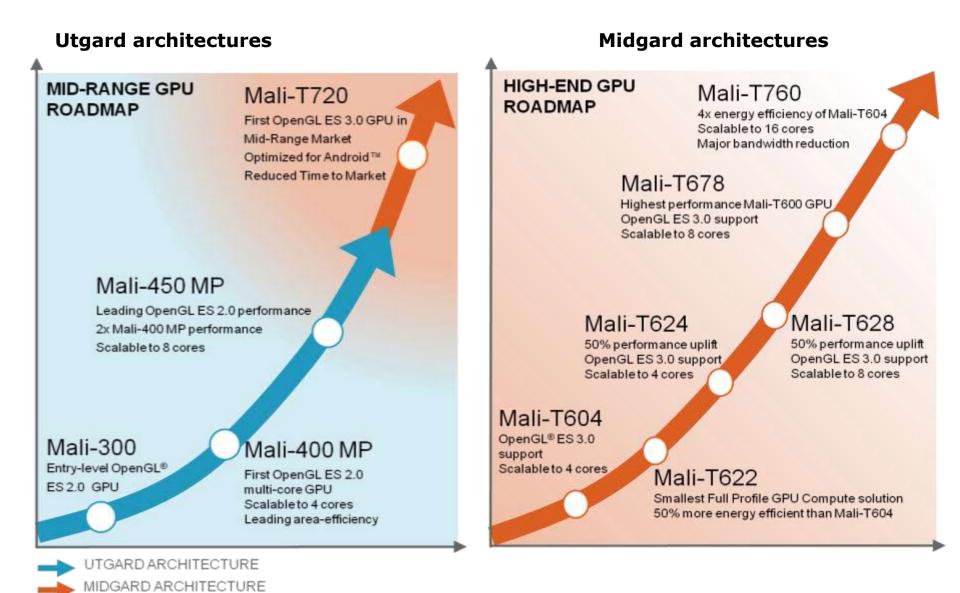

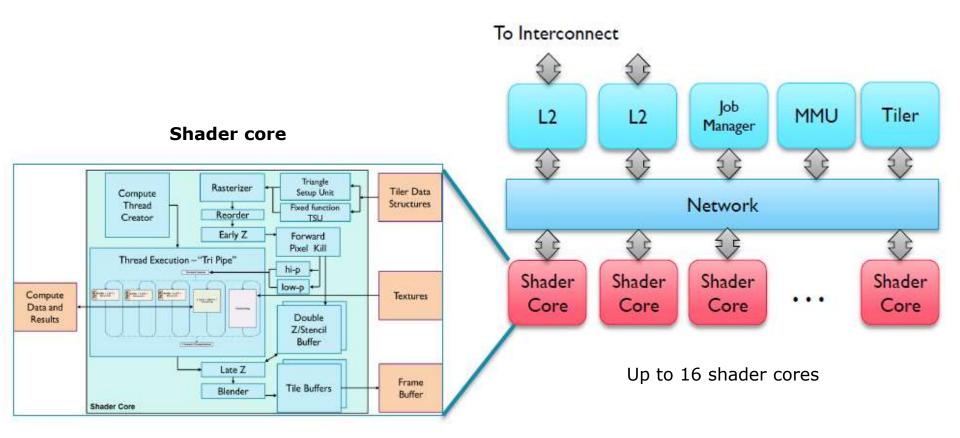

# 5.6 Samsung's first 10 nm SOC: the Exynos 9 8895 (2017)

- 5.6.1 The Exynos 9 Series 8895 Overview

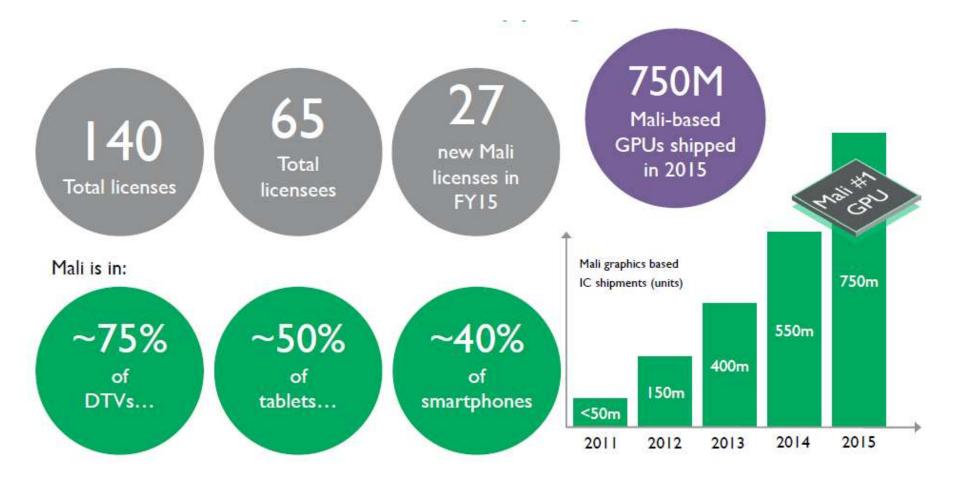

- 5.6.2 Integrating ARM's next generation Mali-G71 GPU that is based on ARM's 3. gen. (Bifrost) GPU architecture

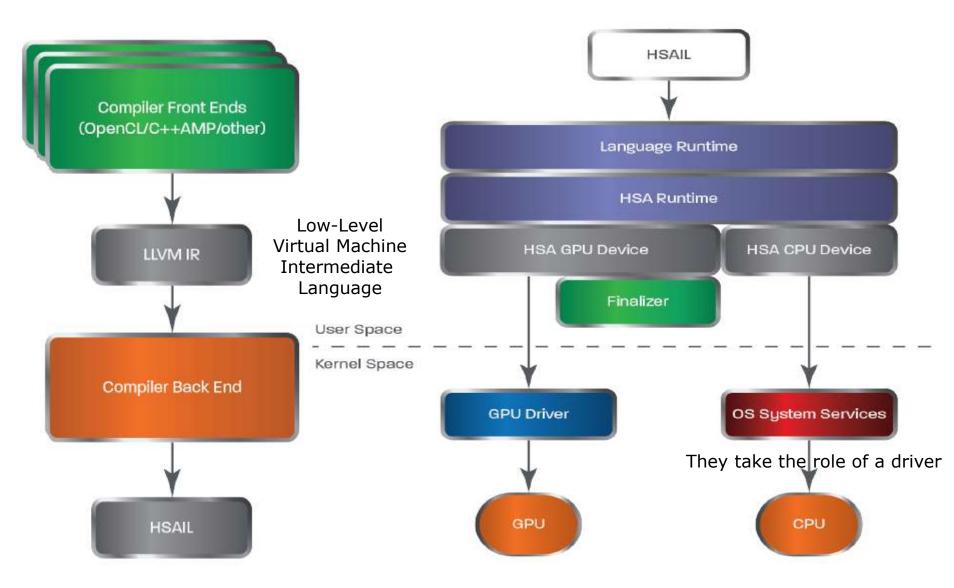

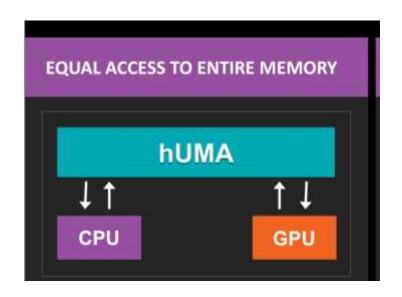

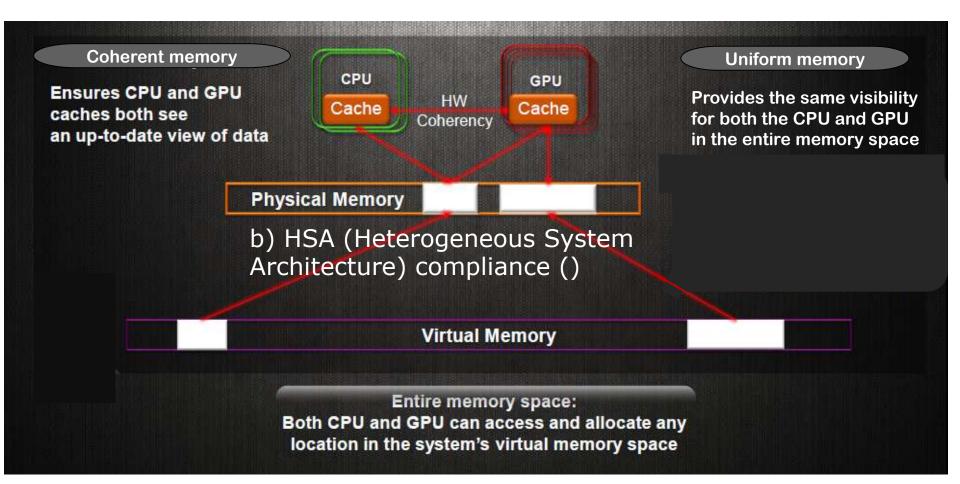

- 5.6.3 HSA (Heterogeneous System Architecture) compliance

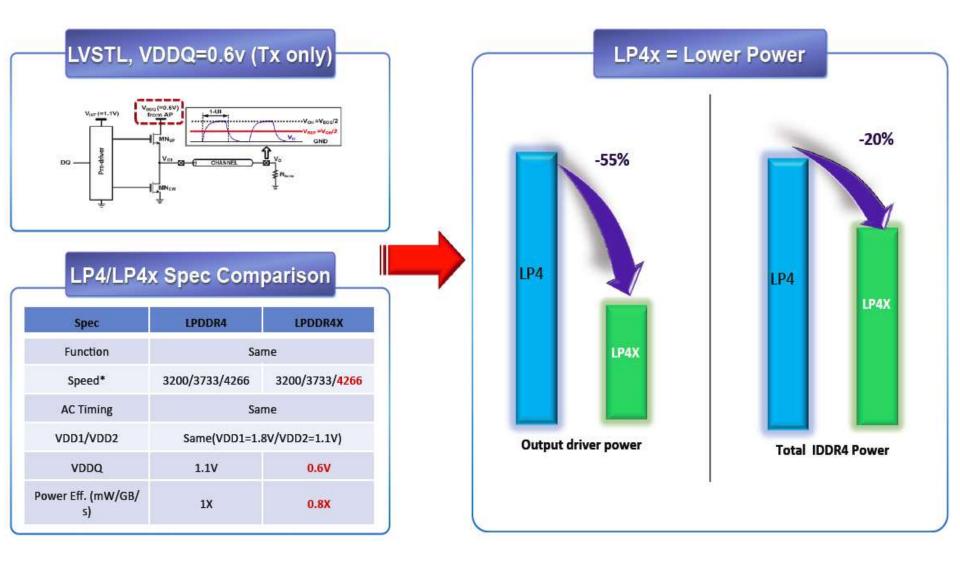

- 5.6.4 Support for LPDDR4x memory

- 5.6.5 Separate security processing unit

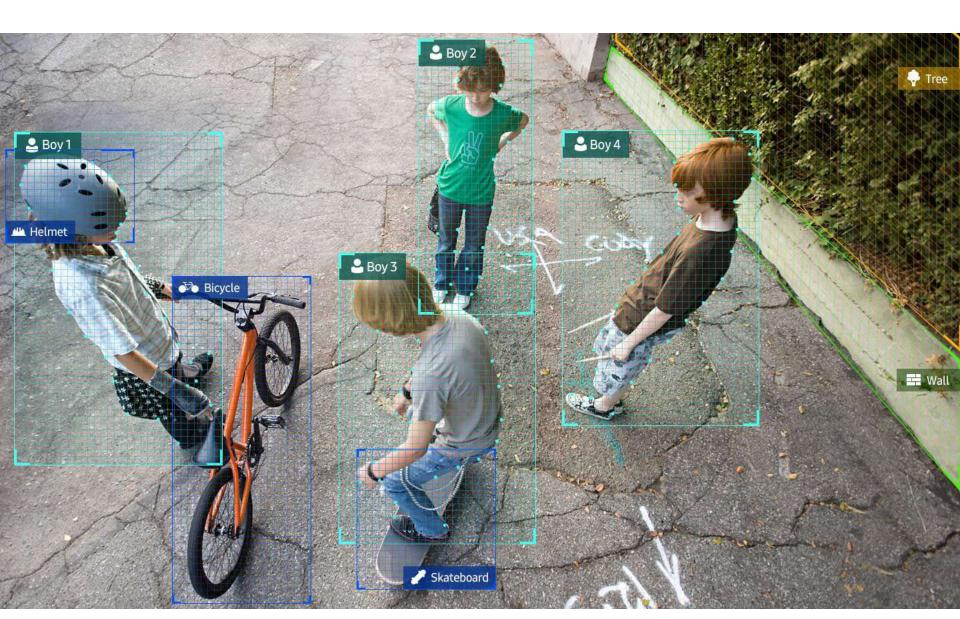

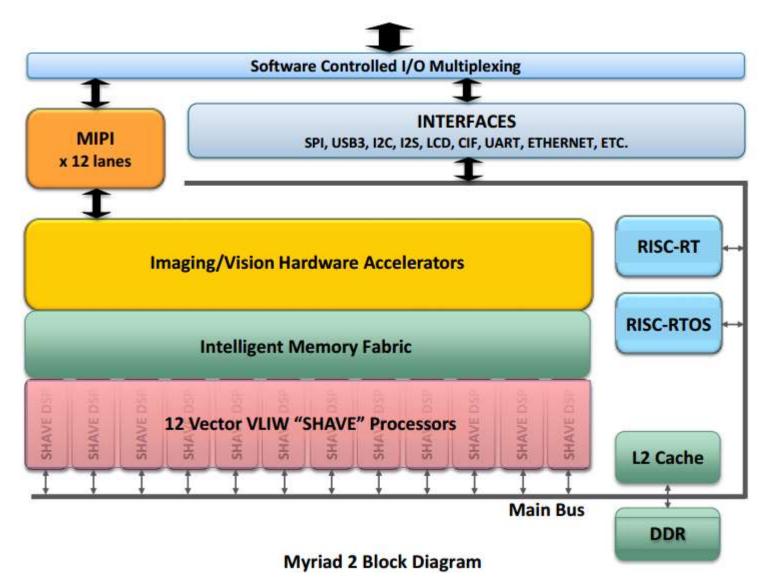

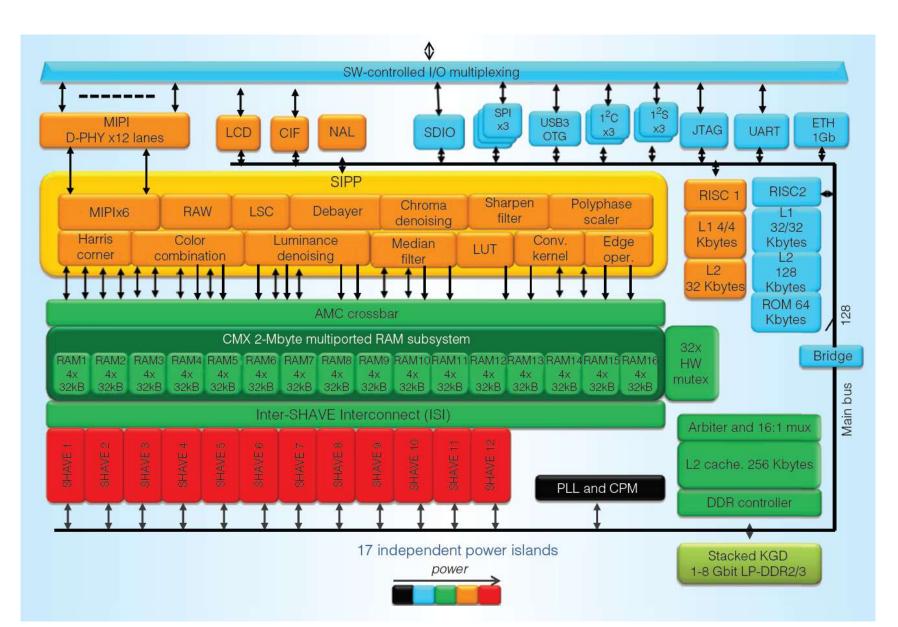

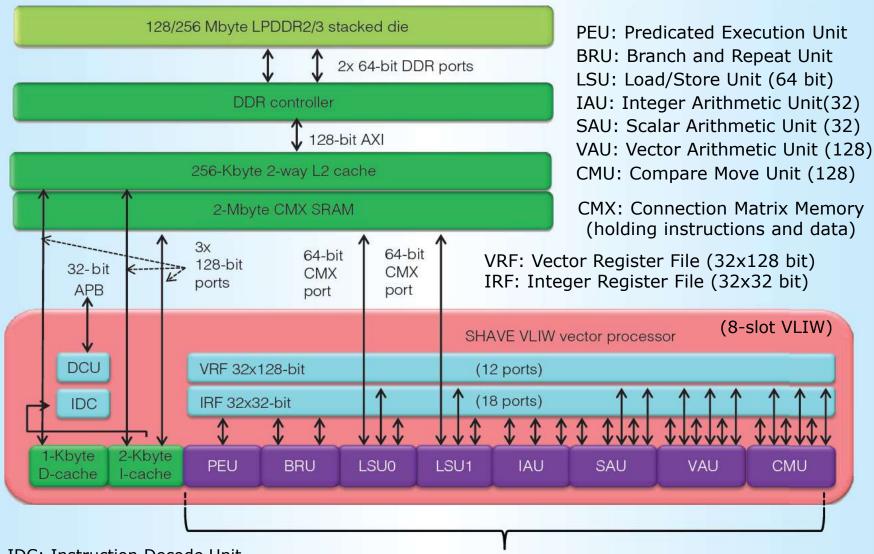

- 5.6.6 Vision Processing Unit (VPU)

# 5.6.1 The Exynos 9 Series 8895 - Overview

### 5.6.1 The Exynos 9 Series 8895 - Overview

- It is Samsung's first SoC fabricated on their 10 nm FinFET process.

The 10nm FinFET process allows up to 27% higher performance or 40% lower power consumption when compared to 14nm LPE FinFET [30].

- It is the kernel piece of one alternative of Samsung's Galaxy S8, S8+.

The other alternative is using Qualcomm's Snapdragon 835 for these mobiles (sold in the US).

- It was announced in 02/2017 and shipped in 04/2017.

# Main features of Samsung's Exynos 9 Octa 8895 (2017)