## Morgan Stanley

# **IDF**2009

#### INTEL DEVELOPER FORUM

PROCESSOR ARCHITECTURE AND HPC POINT OF VIEW

## Zoltan Juhasz

zoltan.juhasz@morganstanley.com

Agenda

- Few quotes from the Keynotes at IDF

- Intel Server / Desktop Roadmap

- Key Points of Intel Nehalem Based Platforms

- Intel Advanced Vector eXtension (AVX) introduction

- Intel **Nehalem-EX** architecture: features and benefits

- HP Extreme Scale Computing: Server Futures (near term)

## Keynotes from IDF

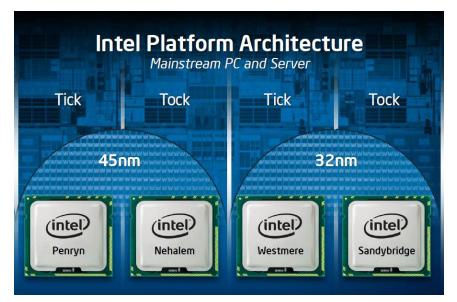

- Intel Platform Architecture: Tick-Tock / next gen. silicon architecture new microarchitecture

- Intel is aggressively expanding to the embedded world

- Intel Platform Choice for Mission Critical Servers: Nehalem-EX

- Improved energy efficiency, and dissipation is another key area for Intel

- New silicon technology: 32nm (Q4 2009)

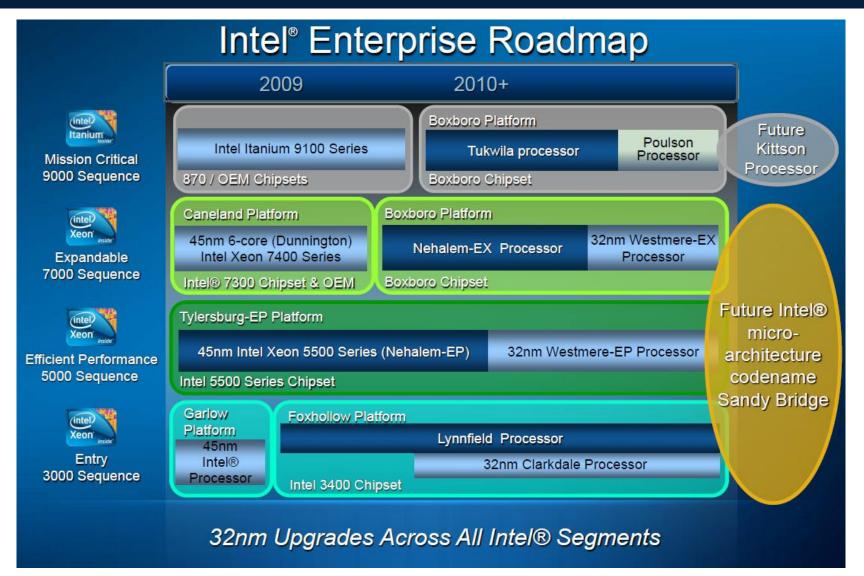

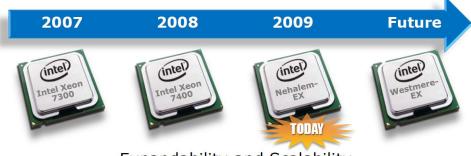

#### Keynotes: Server Roadmap

#### Keynotes: Client Roadmap

|                                                    | 2009                                                                                                                       | 2010+                                                                               |                                                     |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------|

| Desktop Extreme /<br>High-End Desktop              | X58 Platform<br>Intel® Core i7 Extreme Processor (4C/8T)<br>Intel® Core i7 Processor (4C/8T)<br>Intel® X58 Express Chipset | 2010 HEDT Platform<br>32nm Gulftown Processor (6C/12)<br>Intel® X58 Express Chipset |                                                     |

| Desktop<br>Performance /<br>Mainstream             | Piketon / Kings Creek Platforms   McCreary<br>Platform   45nm Intel®<br>Processor   Intel 5 series Chipset                 | 2C/4T)                                                                              | Future Intel®<br>micro-<br>architecture<br>codename |

| Mobile<br>Extreme /<br>Performance /<br>Mainstream | Calpella Platform<br>Santa Rosa<br>& Montevina<br>45nm Intel®<br>Processor<br>Intel 5 series-M Chipset                     | 2C/4T)                                                                              | Sandy Bridge                                        |

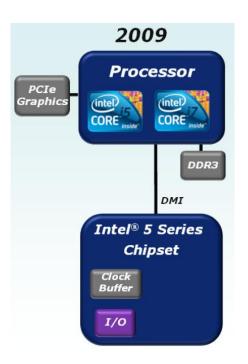

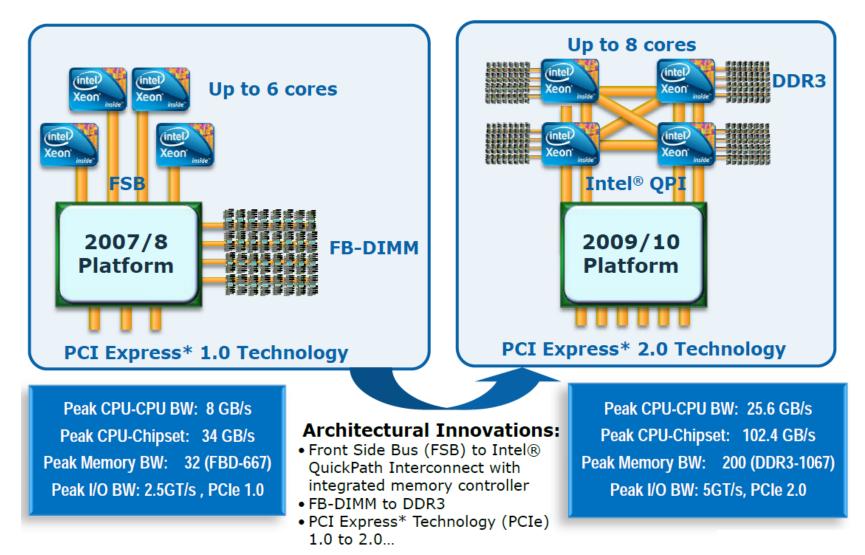

## Intel Nehalem Based Platforms

- Intel Hyper-Threading Technology

- Intel Turbo Boost Technology

- PCI Express interface moves to the processor

| l i in | tegrated M | emory Cor  | ntroller i i |

|--------|------------|------------|--------------|

|        |            |            |              |

| Core   | Core       | Cor        | e Core       |

|        |            |            |              |

|        |            |            |              |

| P Inte | l® Smart C | ache - Sha | ared L3      |

# "Any sufficiently advanced technology is indistinguishable from magic."

Arthur C. Clarke, "Profiles of The Future", 1961 (Clarke's third law)

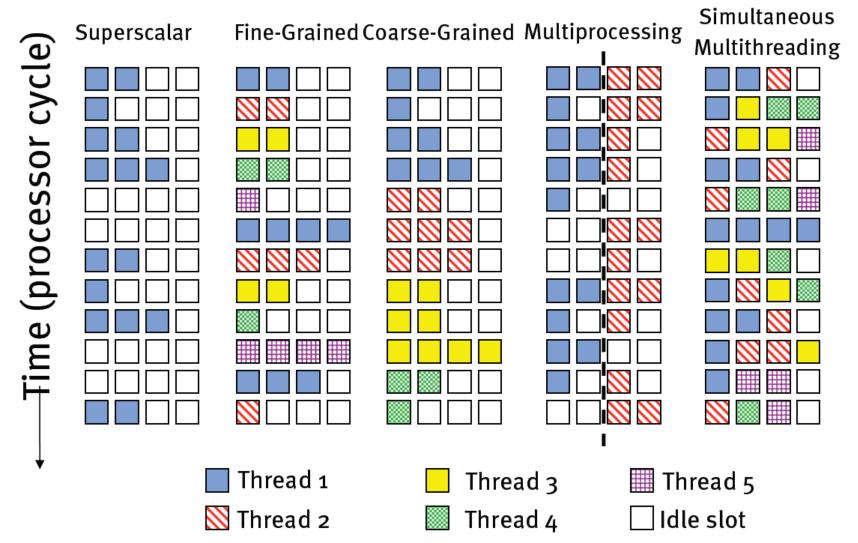

## Multithreaded Categories

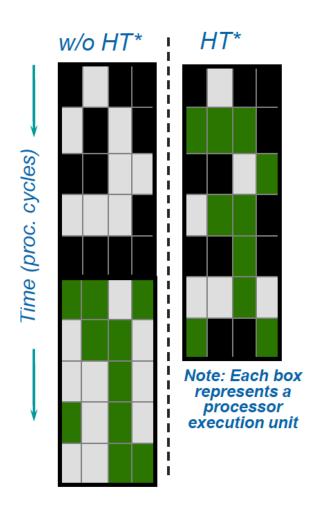

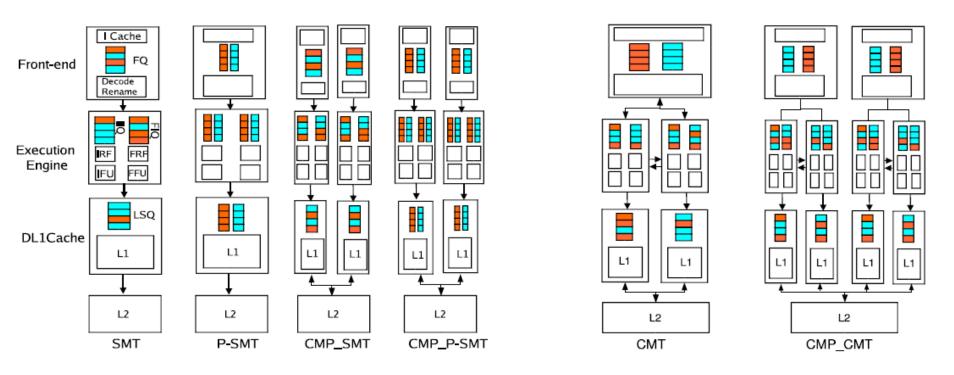

## SMT – partitioned / clustered

Difference lies is in the design decision what is

- replicated (register renaming logic, instruction pointer, ITLB, etc.)

- partitioned (reorder buffers, load/store buffers, various queues)

- shared (caches, micro architectural registers, execution units)

Will not help if one thread monopolizes shared resources, cache effects etc.

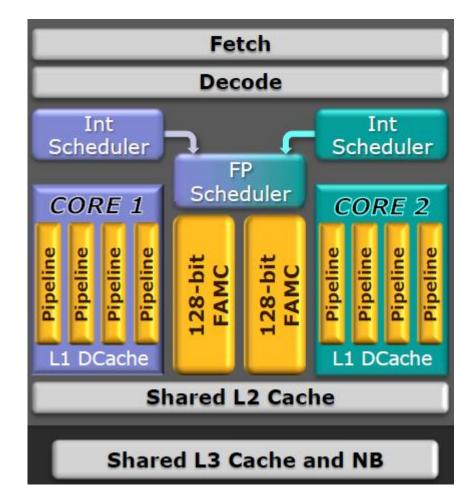

## AMD Bulldozer

- Bulldozer implements a Cluster(-based) multiprocessing (CMT)

- Integrates two superscalar processors

- 2 Flexible Floating Point FAMC unit that can be dedicated or shared between the two core per cycle

- Independent integer and FP schedulers are provided

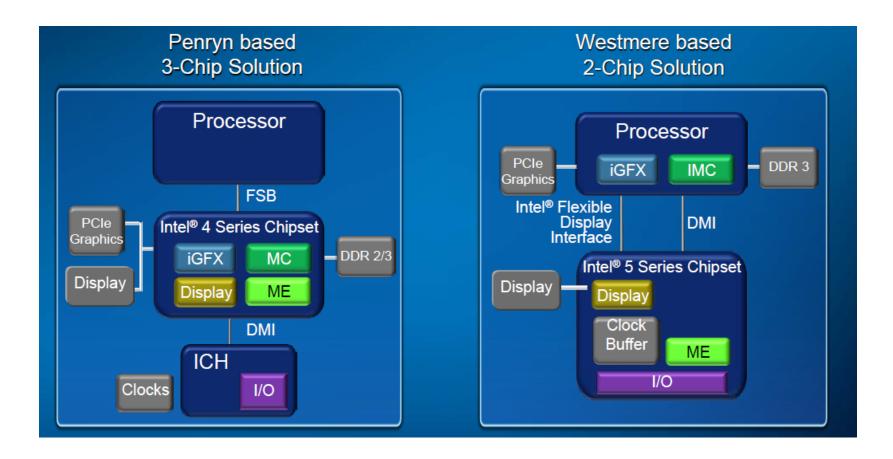

#### Keynotes: Intel Flexible Display Interface

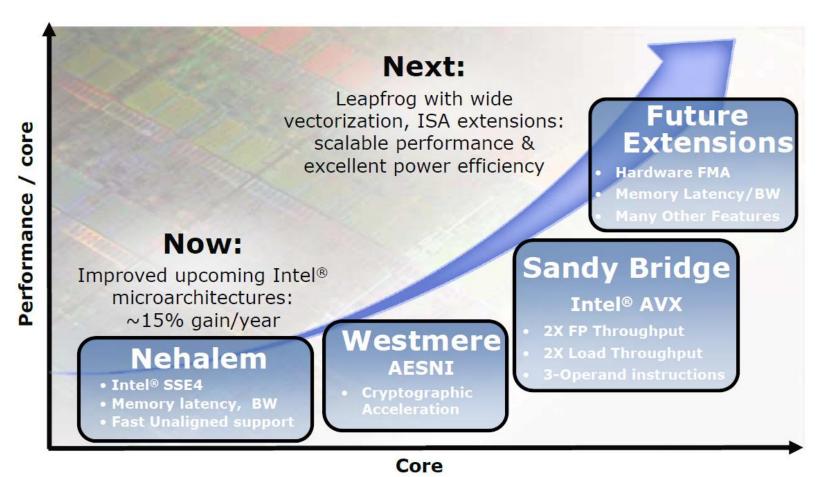

## Intel Advanced Vector Extensions (AVX)

• Intel Sandy Bridge Microarchitecture features Intel Advanced Vector Extension

YMMO

**XMMO**

## Intel AVX Key features and benefits

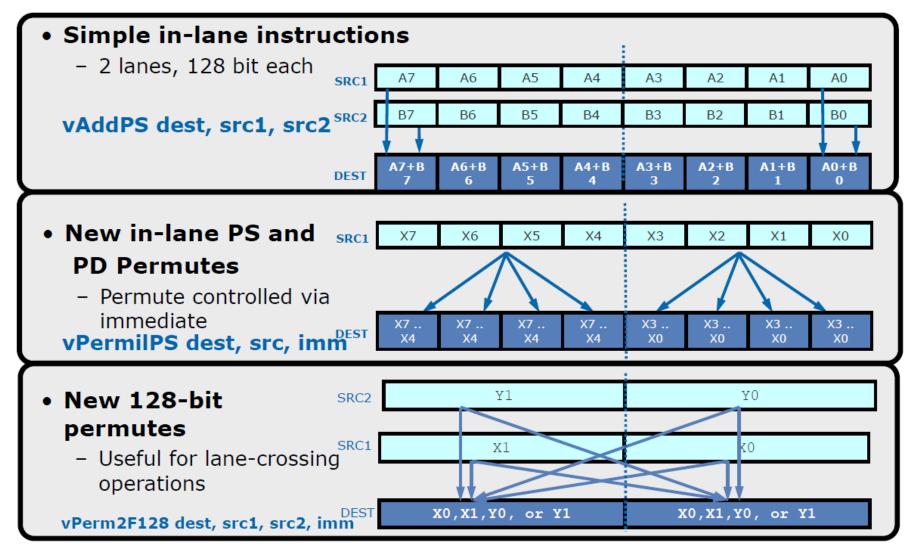

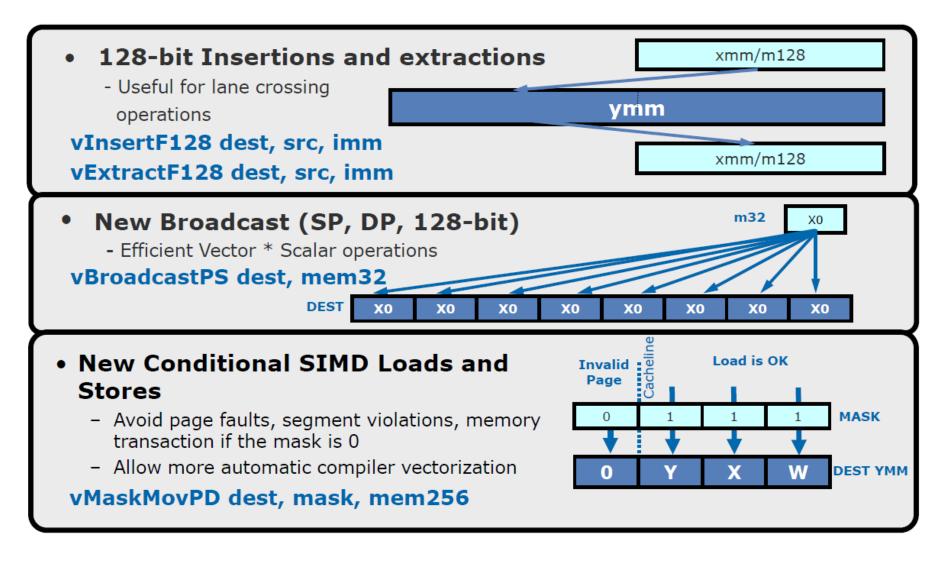

- Wider Vectors (128 to 256 bit with 2 128-bit load ports)

- Enhances Data Rearrangement (broadcast, mask loads and permute data)

- Flexible unaligned memory access Support (e.g. no penalty for unalgined loads on aligned memory)

- Mixing AVX / SSE code may incur penalty (AVX 256 dirties upper 128 bits)

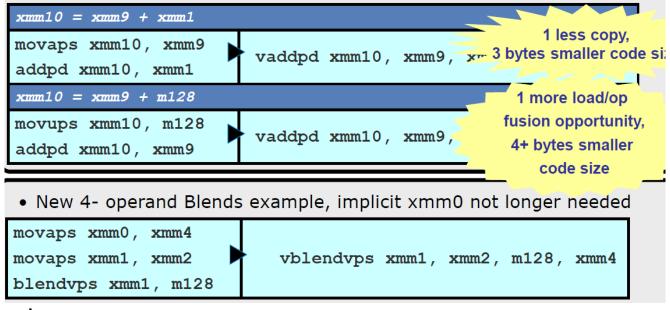

- A new 3- and 4- operand instruction format:

## Intel AVX New Primitives

## **Intel AVX New Primitives**

## Intel AVX software support

- Intel Compiler: 11.1

- Intel IPP 6.1

- Intel MKL 10.2

- Intel TBB 2.2

- GNU GCC 4.4.1

- Microsoft Visual Studio 2010 Beta 2

- Update on Fused Multiply Add: Not supported on Sandy Bridge Microarchitecture

## Intel Nehalem-EX Architecture

- Scalable Nehalem-EX Architecture

- Reliability, Availability and Serviceability (RAS)

- The platform for x86-64 High-End Computing

- Several uncore improvements

Expandability and Scalability Reliability, Availability, and Serviceability (RAS)

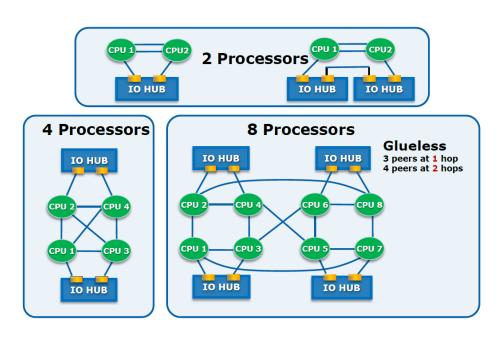

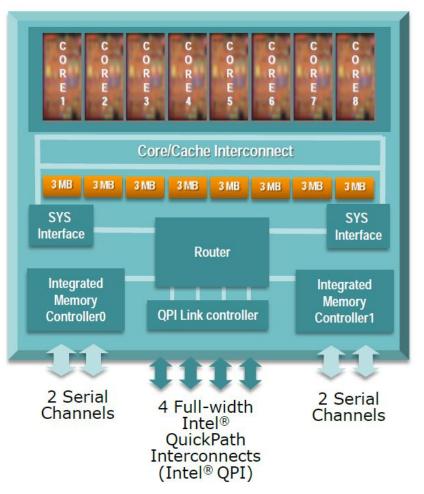

## Scalable Processor Cores

- Up to 8 cores per socket

- 24 MB shared last level cache

- 2,4 and up to 8+ processors

## Platform Capability Enhancement

## Power Optimization / Energy efficiency

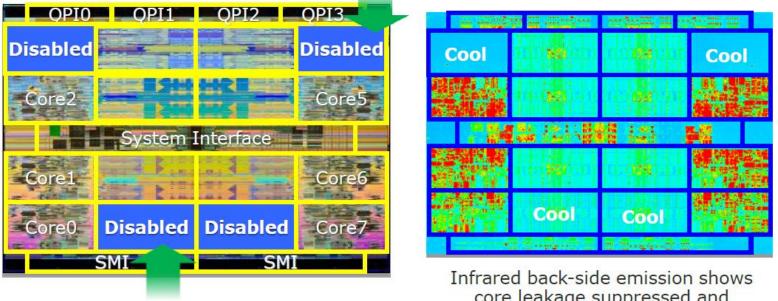

#### Leakage Control at Core and Cache Level

New to NHM-EX: Power gating disabled cores

Power gating disabled cache

core leakage suppressed and cache leakage reduced

Core Level: 40x leakage reduction when shut off Cache Level: 35% during sleep & 83% when shut off

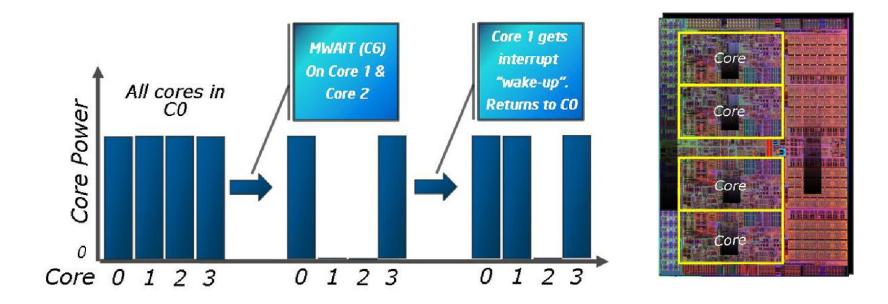

## **Reducing Idle Power Consumption**

- OS initiates C-state en entry by Mwait instruction

- C-states "idle" states

- Different C states means different exit latency

- Windows CPU Power Management Framework (Windows 7)

- P-states "active" states (CO)

| ]                 |

|-------------------|

|                   |

|                   |

|                   |

| 1<br>Cn           |

| Exit Latency (us) |

|                   |

#### Deep Power Down Technology (C6)

- Integrated Power Gate enables a per core C6 state and individual cores transition to a ~OW Power State

- Uncore logic? When all cores in C6, package can transition to C6

#### Near-Term Server Futures

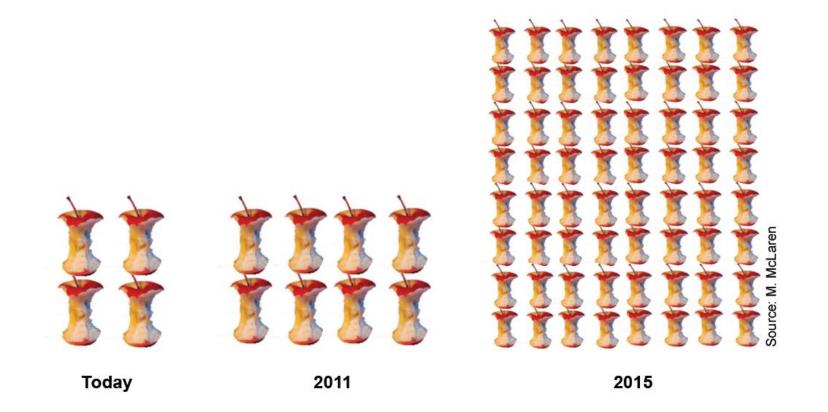

## All you need to know about Multi-Core

#### Company server architecture

- HPC segment is moving towards high density commodity hardware

- Past: 2-socket server (2+2 / 4+4 cores), P4 / Opteron processors

- Now: 2-socket servers (4+4 cores), Core2 architecture

- Future: 2-socket servers (4+4 / 6+6 cores), Nehalem / Westmere architecture

- Focus: best performance per unit price, not absolute performance

#### What Are The New Cores Like?

- Just like old ones

- Clock rates NOT going up

- Incore improvements: more FLOPS/tick, better virtualization support, HTT

- Uncore improvements: integrated memory controllers, etc.

- Takes a little pressure off of memory latency

- Memory used to grow twice as distant (in clocks) every eighteen months

- Does not take pressure off of memory bandwidth

- **Bandwidth**: 0.5B/FLOP is 'good' for HPC

- Nehalem gives us 40 GB/s : (3Ghz \* 4 F/tick \* 4 cores \* 2 sockets ) = 0.4

- Capacity: up to 1.5, 3, 6GB/core (48GB in a 2s-4c system)

#### Prognostication

- Nealem: wonderful gift of memory bandwidth

- 1.3x 3x performance boost

- Core count ++ means lower bandwidth/core

- Westmare @ 6 cores

- Nehalem-EX @ 8 cores, but more bandwidth

Reliability, Availability, and Serviceability (RAS)

## **Evolutionary Improvements Running Out of Gas**

#### • S/W has been relying on H/W improvements

- Moore's Law hid inefficiencies

- "Every programmer's job is to consume twice as much compute power every eighteen moths!"

- Get three programmers together, and they'll first have to define nine levels of abstraction to ensure optimal job security.

#### • S/W needs to be come more efficient

- Requires effort and expertise from S/W part

- Olukotun's view 3 real dimensions of processor performance:

- clock frequency

- superscalar instruction issue

- multiprocessing

- First two have been pretty much exhausted, programmers need to switch.

## The Memory Wall

#### • 2014: assume 400GF mainstream processor

- Aggressively multi-core

- 0.5 B/FLOP means 200 GB/s, ~10x today's chips

- Opinion: won't happen in copper

- Optical connection

- Stacked memory (more levels)

- ?

- ... maybe the hardware folks can save your sorry selves once again!

#### Morgan Stanley

Q/A

29